CHAMP-AV8 (VPX6-462) H

ARDWARE

U

SER

’

S

M

ANUAL

C

URTISS

-W

RIGHT

II

P

ROPRIETARY

826448 V

ERSION

5 M

ARCH

2015

V

ERSION

H

ISTORY

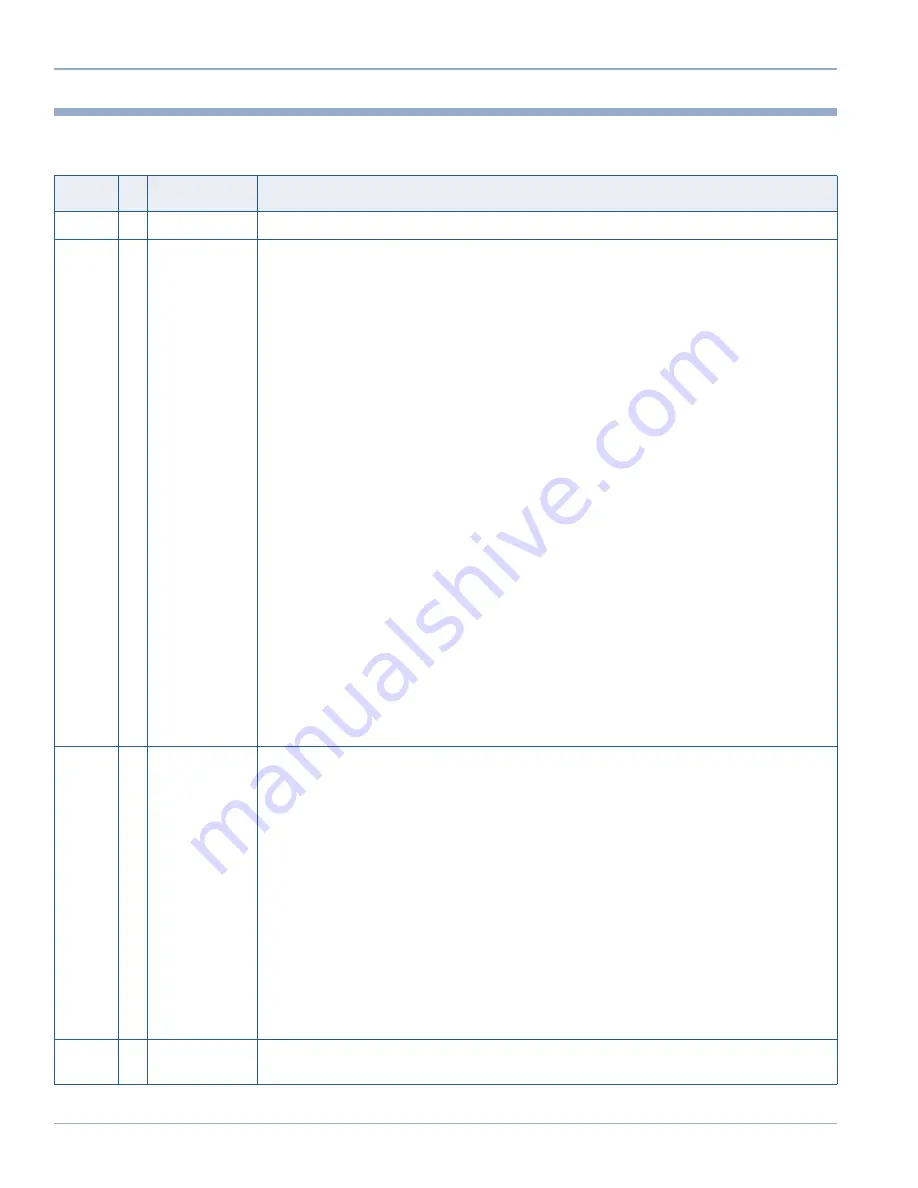

Version By Date

Description

1

JP July 2011

First release.

2

TM September 2012 Updated document template.

Updated section, “General Description” on page 1-2.

Updated section, “Feature Summary” on page 1-3.

Updated Figure 1.2, “CHAMP-AV8 Functional Block Diagram,” on page 1-5.

Updated “Quad-Core Intel Core i7 Processors” on page 1-6.

Updated Figure 1.3, “CHAMP-AV8 PCI Express Distribution,” on page 1-7.

Updated section, “PCI Express Architecture” on page 1-7.

Updated Table 1.1 on page 1-8.

Updated Figure 1.5, “CHAMP-AV8 SRIO Port Connections,” on page 1-11.

Updated section, “Core Functions FPGA” on page 1-12.

Updated section, “Double Data Rate (DDR3) SDRAM with ECC” on page 1-13.

Updated section, “Protected Boot Flash Memory” on page 1-14.

Updated section, “NAND Flash Memory” on page 1-14.

Updated section, “Non-Volatile RAM (NVRAM)” on page 1-15.

Updated section, “Interrupt Controller” on page 1-24.

Updated section, “Specifications” on page 1-31.

Updated Table 1.8, “CHAMP-AV8 Weight,” on page 1-33.

Updated Table 1.9, “VPX6-462-A Air-Cooled Ruggedization Levels,” on page 1-34.

Updated section “Mezzanine Module Power Considerations” on page 2-5.

Updated Table 2.2, “Maximum Supply Current for XMC Site,” on page 2-5.

Updated section “Installation Checklist” on page 3-3.

Updated section “Choose a VPX Slot Location” on page 3-4.

Replaced Figure 3.2, “System Boot Screen,” on page 3-11.

Updated section “Display the Initial Screen Message” on page 3-13.

Replaced Figure 3.3, “GRUB Loading Message,” on page 3-13.

Updated section, “Troubleshooting” on page 3-14.

Updated Table 3.7, “Summary of LED Behavior,” on page 3-15.

Updated Appendix A, "Connector Pin Assignments".

Added Appendix B, "Statement of Memory Volatility".

Added Appendix C, "Memory Write Protection".

3

JP February 2013

Updated Figure 1.2, “CHAMP-AV8 Functional Block Diagram,” on page 1-5.

Updated section “PCI Express Architecture” on page 1-7.

Updated Table 1.1, “XMC/Expansion Plane Interface Build-Time Options for PCIe,” on page 1-8

Added Figure 1.4, “PCIe Switch Partitions,” on page 1-9.

Updated section “SRIO Fabric” on page 1-10.

Updated section “XMC Site” on page 1-15.

Updated section “RTC/CMOS RAM Backup Power” on page 1-24.

Updated Table 1.6, “Power Requirements,” on page 1-32.

Updated section “Continuum IPC™ Library” on page 1-40.

Updated section “Detailed Power Requirements” on page 2-3.

Updated Table 2.1, “Voltage and Current Requirements,” on page 2-3.

Updated “XMC I/O” on page 2-4.

Updated “XMC Site” on page 2-4.

Updated section “Mezzanine Module Power Considerations” on page 2-5.

Updated section “VITA 46 P1 Fabric Connector” on page A-9.

Updated Table A.4, “P0 Utility Connector Signal Definitions,” on page A-15.

Updated Table A.39, “RTM SW2–SW18 Functions,” on page A-57.

4

JP June 2013

Updated “Configuring Jumpers” on page 2-7.

Updated Table A.39, “RTM SW2–SW18 Functions,” on page A-57.

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com