C

URTISS

-W

RIGHT

P

RODUCT

O

VERVIEW

826448 V

ERSION

5 M

ARCH

2015

P

ROPRIETARY

1-21

LVTTL D

ISCRETE

D

IGITAL

I/O

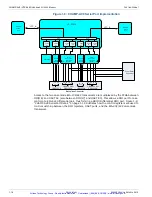

There are 16 Digital I/O (DIO) bits which are accessible at the backplane connector. Each bit

is individually programmable to be an input, output, or I/O. Each bit configured as an input

may be used to trigger an interrupt which is further programmable to be either level or

edge-sensitive. Both levels and transition directions may be detected. Each DIO's input port

contains a filtering function that filters all pulses <= 40 ns. The DIO bits are controlled through

a set of registers in the CF-FPGA. The DIO bit functions can be programmed independently.

The signals for the lower two DIO bits (DIO[1:0]) can be used as the MBSC synchronization

signals as described in the MBSC section. When configured in MBSC mode, the DIO [1:0]

cannot function as DIO.

In addition to performing input and output through the processor data lines, the DIO input

channels can also be routed to the available Local Processor Block Interrupt Controllers. The

DIO registers, together with the Local Processor Block (LPB) interrupt controller, can perform

the DIO interrupt handling solution. DIO pin signal level or edge events can trigger interrupts.

Each active DIO bit must be unmasked and enabled in the CF-FPGA. The CF-FPGA combines

and routes the DIO level interrupts to the appropriate processor interrupt lines.

Each LVTLL I/O line is pulled high to 3.3V with an on-board 10 KOhm resistor located between

a FET-based bus transceiver and the CF-FPGA. The digital I/O lines are 5V tolerant at the

backplane.

For more information on programming the DIO, consult the BSP User's Manual.

EIA-422 D

IFFERENTIAL

D

ISCRETE

D

IGITAL

I/O

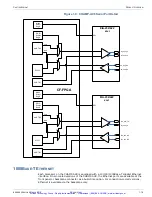

The CHAMP-AV8 provides the capability to control the outputs of the two drivers on the

dual-mode EIA-232/422 transceivers which are normally controlled by UARTs A0/B0. In a

similar fashion, there are registers that can read the state of the EIA-232/422 receivers. In

total there are two inputs and two outputs. Each input may be configured to generate an

interrupt. When configured as discrete differential I/O, the drivers and receivers are used as

general-purpose differential-mode control signals and not as serial EIA-232/422 I/O.

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com