C

URTISS

-W

RIGHT

P

RODUCT

O

VERVIEW

826448 V

ERSION

5 M

ARCH

2015

P

ROPRIETARY

1-11

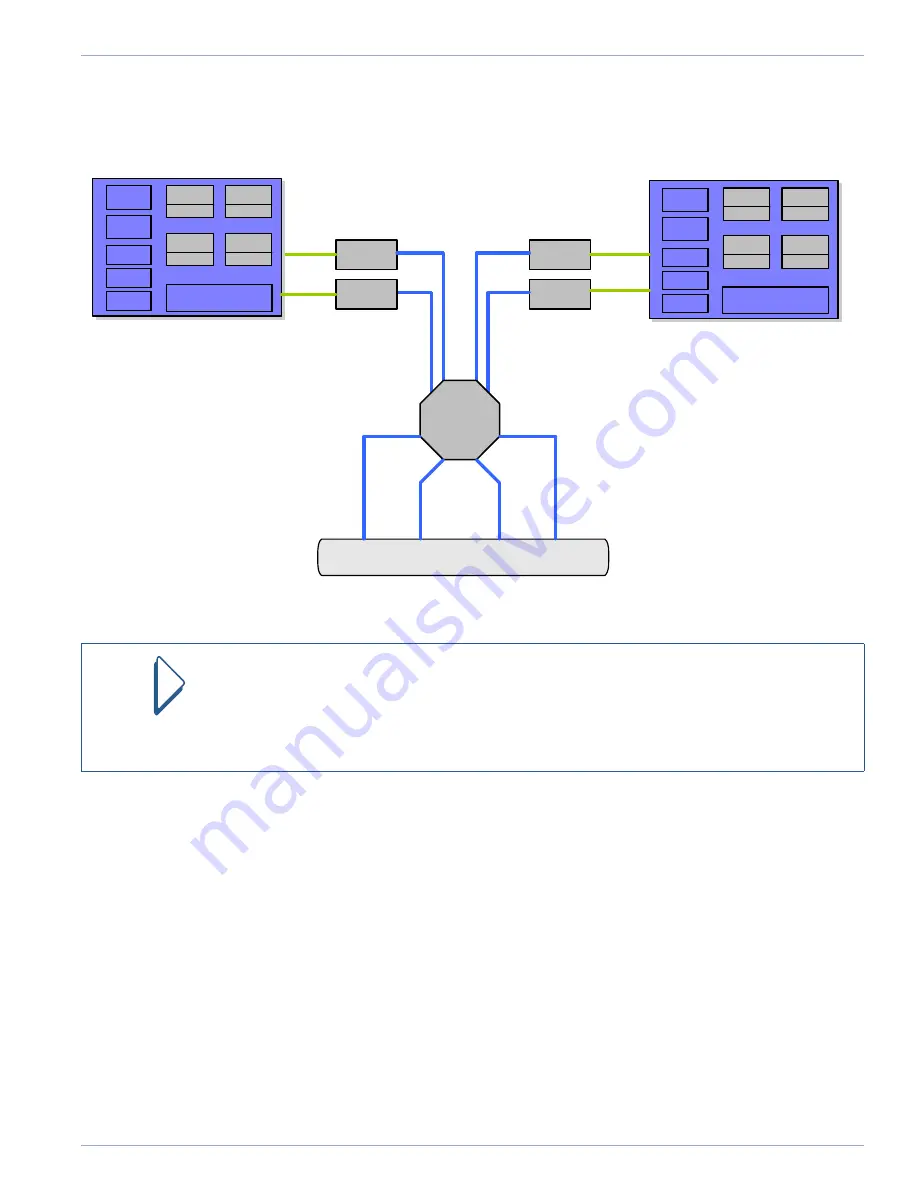

Figure 1.5: CHAMP-AV8 SRIO Port Connections

Note

SRIO connections do NOT auto-negotiate their link operating speed if different generations

of SRIO are mixed. For example, when mixing older hardware boards such as the VPX6-185

or the CHAMP-AV6 (which support Gen 1 speed, 3.125 Gbaud) with the CHAMP-AV8

(defaults to Gen 2, 5.00 Gbaud, but supports 3.125 Gbaud) the off-board SRIO link speed

must be set to values supported on both boards. In this case the CHAMP-AV8 would be

down-graded to the Gen 1 speed. See the BIOS User's Manual, Curtiss-Wright document

826450, for more information.

Node A

Intel Core i7 quad - core

Node A

SDRAM

Control

SDRAM

Control

L3

PCIe

L 1 / L2

Core

L 1 / L2

Core

L 1 / L2

Core

L 1 / L2

Core

PCIe

PCIe

P1 Connector

PCIe-

SRIO

PCIe-

SRIO

PCIe-

SRIO

PCIe-

SRIO

SRIO

Gen2

Switch

x4 SRIO

Node A

SDRAM

Control

SDRAM

Control

L3

PCIe

L 1 / L2

Core

L 1 / L 2

Core

L 1 / L2

Core

L 1 / L2

Core

PCIe

PCIe

1

Node B

Intel Core i7 quad - core

0

3

7

6

4

P1-PA[0:3]

2

5

x4 PCIe

x4 PCIe

#1

#2

#2

#1

P1-PB[0:3]

P1-PC[0:3] P1-PD[0:3]

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com