SERIES IP511 INDUSTRIAL I/O PACK ISOLATED QUAD EIA/TIA-422B COMMUNICATION MODULE

___________________________________________________________________________________________

- 13 -

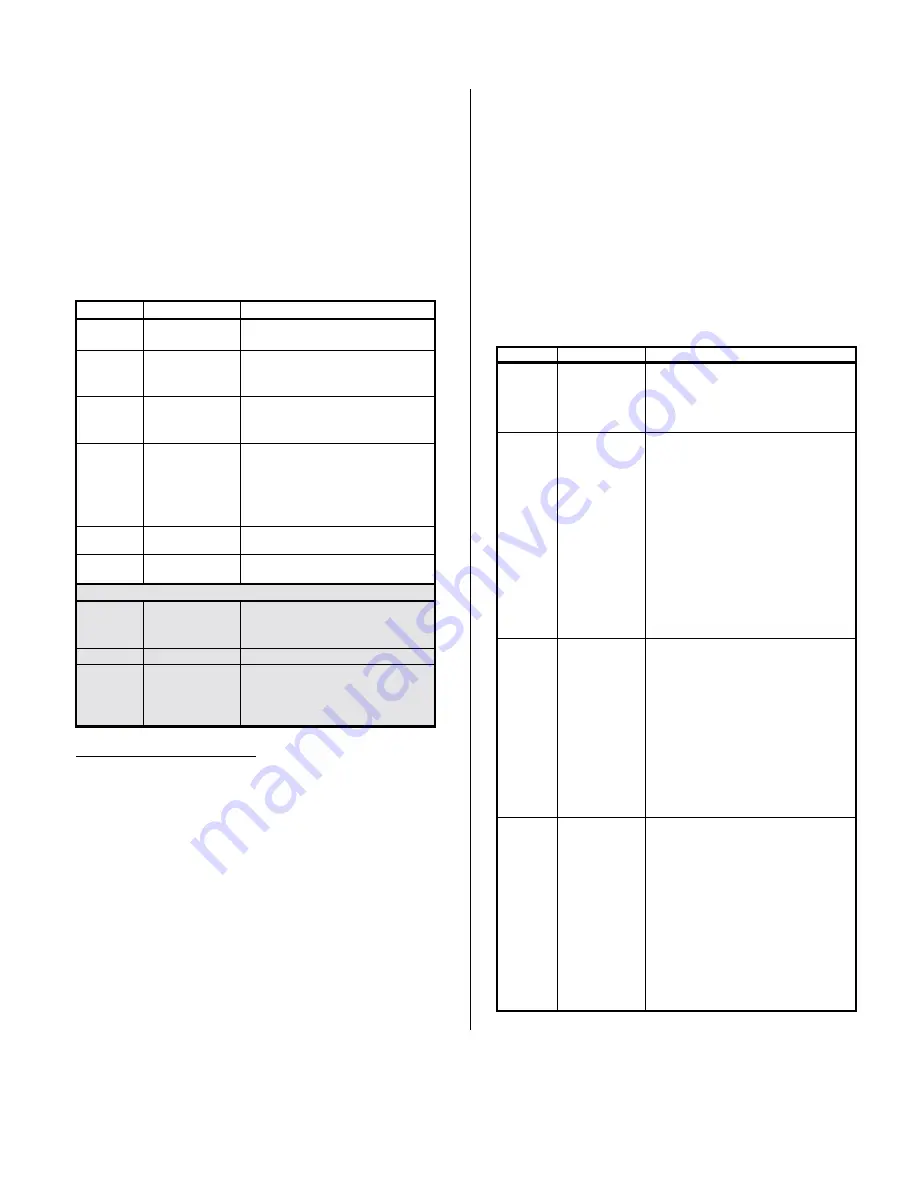

MCR - Modem Control Register, Ports A-D (R/W)

NO FUNCTION FOR MODEL IP511-16

The Modem Control register is normally used to control the

interface with the modem or data set. Since the IP511 does not

implement the DTR and RTS handshake lines, this register is only

functional for Loopback Mode operations as described below, and for

enhanced functions of IP511-64 models.

A power-up or system reset sets all MCR bits to 0 (bits 5-7 are

permanently low on standard units).

Modem Control Register

MCR Bit

FUNCTION

PROGRAMMING

0

Data Terminal

Ready (DTR)

The DTR handshake signal is not

implemented on this model.

1

Request to

Send Output

Signal (RTS)

The RTS handshake signal is not

implemented on this model.

2

Out1 (Internal)

Used in internal Loopback Mode

only. No Effect on External

Operation

3

Out2 (Internal)

Used in internal Loopback Mode

only.

0 = External Serial Channel

Interrupt Disabled

1 = External Serial Channel

Interrupt Enabled

4

Loop

1

0 = Loop Disabled (Normal Mode)

1 = Local Loopback Enabled

5,6,7

Not Used on

standard units

On standard units, these bits are

set to logic 0.

Extended Register Functionality (Model IP511-64 Only)

5

XON Enable

0 = Disable Any XON function

(Standard 16C550 Mode)

1 = Enable Any XON function

6

Rx/Tx I/O Mode

Not Used on IP511 (set to 0)

7

Clock Divide

0 = Normal divide by 1 clock

(8MHz clock baud rates apply)

1 = Divide clock by 4

(2MHz baud rates apply)

Notes (Modem Control Register):

1. MCR Bit 4 provides a local loopback feature for diagnostic testing of

the UART channel. When set high, the UART serial output

(connected to the TXD driver) is set to the marking (logic 1 state),

and the UART receiver serial input is disconnected from the RxD

receiver path. The output of the UART transmitter shift register is

looped back into the receiver shift register input. The four modem

control inputs (CTS, DSR, DCD, & RI) are disconnected from their

receiver input paths. The four modem control outputs (DTR, RTS,

OUT1, & OUT2) are internally connected to the four modem control

inputs (while their associated pins are forced to their high/inactive

state). Thus, in Loopback Mode, transmitted data is immediately

received permitting the host processor to verify the transmit and

receive data paths of the selected serial channel. In Loopback

Mode, interrupts are generated by controlling the state of the four

lower order MCR bits internally, instead of by the external hardware

paths. However, no interrupt requests or interrupt vectors are

served and interrupt pending status is only reflected internally

Note that on Model IP511-64 units, bits 5-7 are programmable only

when the EFR bit 4 is set to “1”. The programmed values for these bits

are latched when EFR bit 4 is cleared, preventing existing software from

inadvertantly overwriting the extended functions. A power-up or system

reset sets all MCR bits to “0”.

LSR - Line Status Register, Ports A-D (Read/Write-Restricted)

The Line Status Register (LSR) provides status indication

corresponding to the data transfer. LSR bits 1-4 are the error

conditions that produce receiver line-status interrupts (a priority 1

interrupt in the Interrupt Identification Register). The line status register

may be written, but this is intended for factory test and should be

considered read-only by the applications software.

Line Status Register

LSR Bit

FUNCTION

PROGRAMMING

0

Data Ready

(DR)

0 = Not Ready (reset low by CPU

Read of RBR or FIFO)

1 = Data Ready (set high when

character received and trans-

ferred into the RBR or FIFO).

1

Overrun Error

(OE)

0 = No Error

1 = Indicates that data in the RBR is

not being read before the next

character is transferred into the

RBR, overwriting the previous

character. In the FIFO mode, it is

set after the FIFO is filled and the

next character is received. The

overrun error is detected by the

CPU on the first LSR read after it

happens. The character in the

shift register is not transferred

into the FIFO, but is overwritten.

This bit is reset low when the

CPU reads the LSR.

2

Parity Error

(PE)

0 = No Error

1 = Parity Error - the received

character does not have the

correct parity as configured via

LCR bits 3 & 4. This bit is set

high on detection of a parity error

and reset low when the host CPU

reads the contents of the LSR. In

the FIFO mode, the parity error is

associated with a particular

character in the FIFO (LSR Bit 2

reflects the error when the char-

acter is at the top of the FIFO).

3

Framing Error

(FE)

0 = No Error

1 = Framing Error - Indicates that

the received character does not

have a valid stop bit (stop bit

following last data bit or parity bit

detected as a zero/space bit).

This bit is reset low when the

CPU reads the contents of the

LSR. In FIFO mode, the framing

error is associated with a

particular character in the FIFO

(LSR Bit 3 reflects the error when

the character is at the top of the

FIFO).