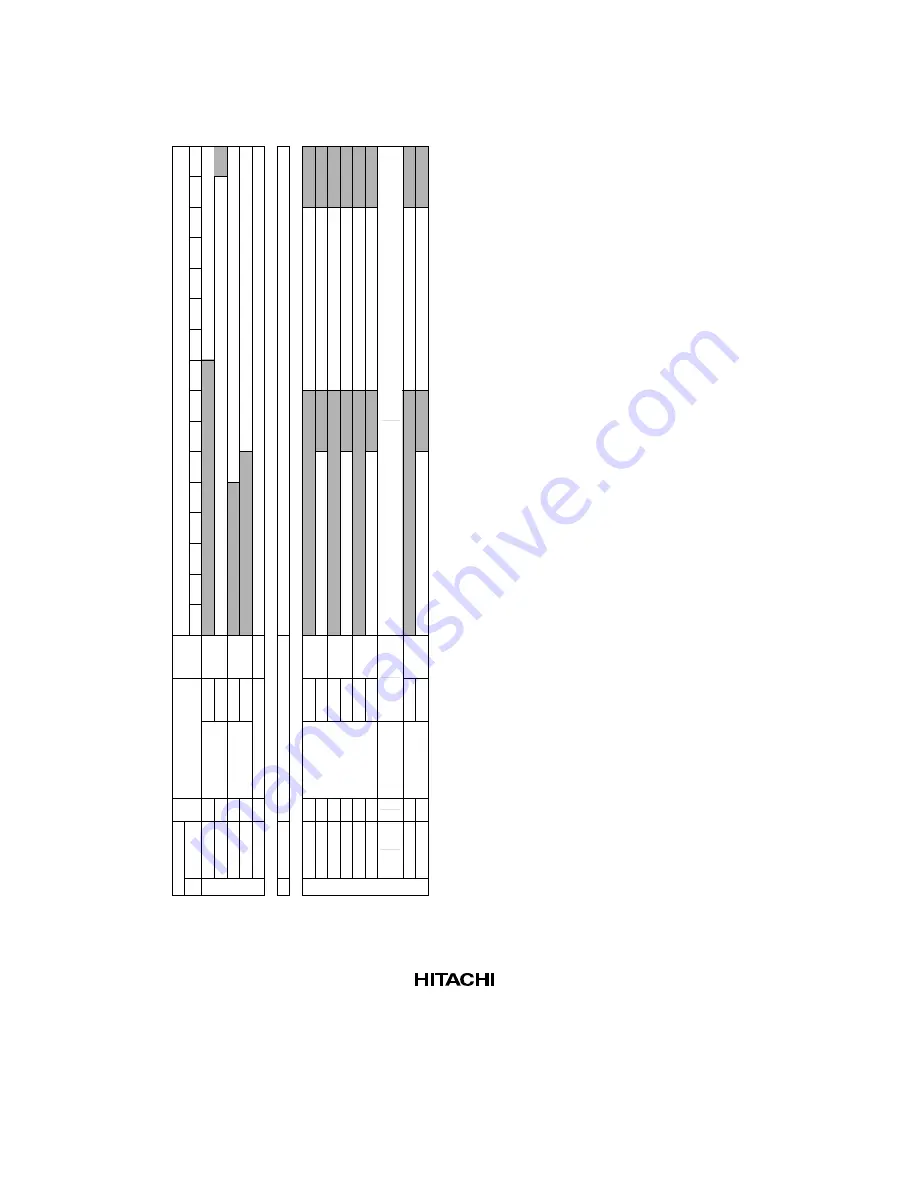

208

Table A-1

Registers (cont)

5. Input Data Control Registers

7. Color Palette

6. Reserved

026 to 0FF

—

Reserved

100

101

102

103

104

105

2FE

2FF

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

0

Color palette

registers

CP000R

CP001R

CP255R

CP002R

R000

B000

R001

B001

B002

R002

R255

B255

G000

G001

G002

G255

000H

000L

001H

001L

002H

002L

255H

255L

R/W

W

R/W

1

5

1

4

1

3

1

2

1

1

1

0

9876543210

Register Address

021

022

023

024

025

R/W

R/W

Register Name

Abbrevia-

tion

R/W

CS1

0

Image data transfer

start address

Image data size

Image data entry

IDER

A [10:1]

1

5

1

4

1

3

1

2

1

1

1

0

9876543210

Data

ISAH

ISAL

IDSX

IDSY

IDE

H

L

X

Y

ISAR

IDSR

Содержание HD64411 Q2

Страница 17: ...10 ...

Страница 31: ...24 ...

Страница 108: ...101 Example 0 0 Work coordinates Rendering coordinates XC YC ...

Страница 110: ...103 Example Old XC YC Old XC XC old YC YC 0 0 Work coordinates Rendering coordinates XC YC ...

Страница 112: ...105 Example 0 0 Work coordinates Rendering coordinates XO1 YO1 XO1 DX2 YO1 DY2 XO1 DX1 YO1 DY1 LINE ...

Страница 116: ...109 Example 0 0 Work coordinates Rendering coordinates XMIN YMIN XMAX YMAX ...

Страница 118: ...111 Example 0 0 Work coordinates Rendering coordinates XMAX YMAX ...

Страница 120: ...113 Example 0 0 Work coordinates XMIN YMIN XMAX YMAX ...

Страница 129: ...122 ...

Страница 167: ...160 ...

Страница 179: ...172 ...

Страница 213: ...206 Figure 7 20 TV Sync Mode Display Timing When DOT 0 or DOT 1 and EXHSYNC cycle is even multiple of CLK1 cycle ...