201

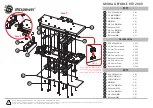

7 . 5 . 1 0 Master Mode Display Timing

T1

CLK1 (input)

(DOT = 0)

CLK1 (input)

(DOT = 1)

DCLK (output)

FCLK (output)

DD17 to DD0

(output)

t

DCRD

T1

T1

t

DCRD

t

FCFD

t

FCRD

t

FCRD

HSYNC

(output)

t

DDH

t

DDS

VSYNC

(output)

t

HSDD

t

HSDD

ODDF (output)

t

VSDD

t

VSDD

CSYNC

(output)

t

SYDD

t

SYDD

DISP (output)

t

DIDD

t

DIDD

CDE (output)

t

CDEDD

t

CDEDD

t

ODDD

t

ODDD

Figure 7-16 Master Mode Display Timing

Содержание HD64411 Q2

Страница 17: ...10 ...

Страница 31: ...24 ...

Страница 108: ...101 Example 0 0 Work coordinates Rendering coordinates XC YC ...

Страница 110: ...103 Example Old XC YC Old XC XC old YC YC 0 0 Work coordinates Rendering coordinates XC YC ...

Страница 112: ...105 Example 0 0 Work coordinates Rendering coordinates XO1 YO1 XO1 DX2 YO1 DY2 XO1 DX1 YO1 DY1 LINE ...

Страница 116: ...109 Example 0 0 Work coordinates Rendering coordinates XMIN YMIN XMAX YMAX ...

Страница 118: ...111 Example 0 0 Work coordinates Rendering coordinates XMAX YMAX ...

Страница 120: ...113 Example 0 0 Work coordinates XMIN YMIN XMAX YMAX ...

Страница 129: ...122 ...

Страница 167: ...160 ...

Страница 179: ...172 ...

Страница 213: ...206 Figure 7 20 TV Sync Mode Display Timing When DOT 0 or DOT 1 and EXHSYNC cycle is even multiple of CLK1 cycle ...