78

3.3.5

Interrupt Operations

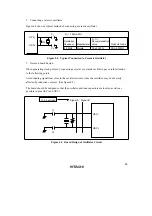

Interrupts are controlled by an interrupt controller. Figure 3.2 shows a block diagram of the

interrupt controller. Figure 3.3 shows the flow up to interrupt acceptance.

Interrupt controller

Priority decision logic

Interrupt

request

CCR (CPU)

I

External or

internal

interrupts

External

interrupts or

internal

interrupt

enable

signals

Figure 3.2 Block Diagram of Interrupt Controller

Interrupt operation is described as follows.

•

When an interrupt condition is met while the interrupt enable register bit is set to 1, an

interrupt request signal is sent to the interrupt controller.

•

When the interrupt controller receives an interrupt request, it sets the interrupt request flag.

•

From among the interrupts with interrupt request flags set to 1, the interrupt controller selects

the interrupt request with the highest priority and holds the others pending. (Refer to table 3.2

for a list of interrupt priorities.)

•

The interrupt controller checks the I bit of CCR. If the I bit is 0, the selected interrupt request

is accepted; if the I bit is 1, the interrupt request is held pending.