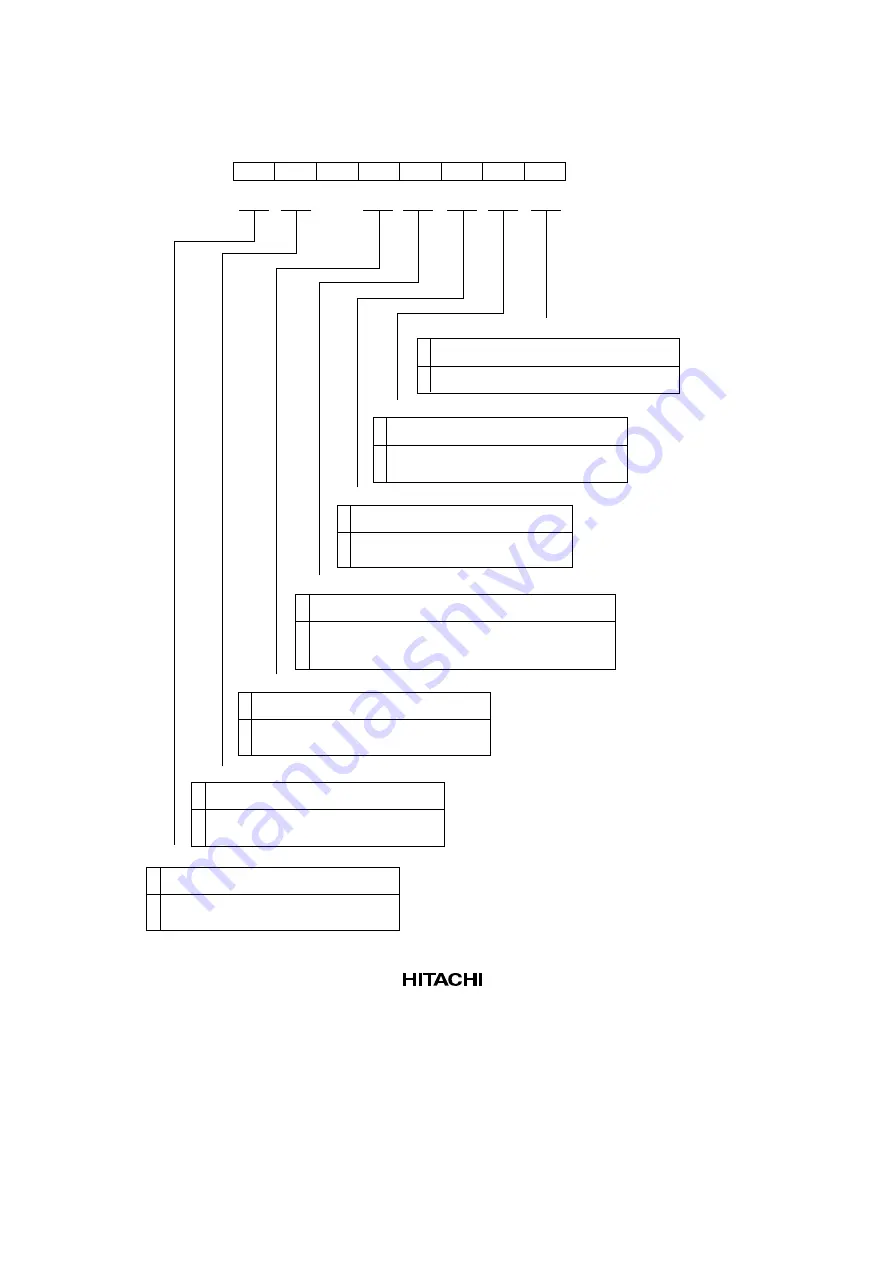

444

IRR2—Interrupt request register 2

H'F7

System control

Bit

Initial value

Read/Write

7

IRRDT

0

R/(W)

*

6

IRRAD

0

R/(W)

*

5

—

0

R/W

3

IRRTFH

0

R/(W)

*

0

IRREC

0

R/(W)

*

2

IRRTFL

0

R/(W)

*

1

IRRTC

0

R/(W)

*

4

IRRTG

0

R/(W)

*

Timer G interrupt request flag

Timer C interrupt request flag

0

Clearing conditions:

When IRRTG = 1, it is cleared by writing 0

1

Setting conditions:

When the TMIG pin is designated for TMIG input and

the designated signal edge is input

Note:

*

Bits 7, 6 and 4 to 0 can only be written with 0, for flag clearing.

A/D converter interrupt request flag

0

Clearing conditions:

When IRRAD = 1, it is cleared by writing 0

1

Setting conditions:

When the A/D converter completes conversion and

ADSF is reset

Direct transition interrupt request flag

0

Clearing conditions:

When IRRDT = 1, it is cleared by writing 0

1

Setting conditions:

When a SLEEP instruction is executed while DTON is

set to 1, and a direct transition is made

Timer FH interrupt request flag

0

Clearing conditions:

When IRRTFH = 1, it is cleared by writing 0

1

Setting conditions:

When counter FH and output compare register FH match

in 8-bit timer mode, or when 16-bit counters FL and FH

and output compare registers FL and FH match in 16-bit timer mode

Timer FL interrupt request flag

0

Clearing conditions:

When IRRTFL = 1, it is cleared by writing 0

1

Setting conditions:

When counter FL and output compare register FL

match in 8-bit timer mode

Asynchronous event counter interrupt request flag

0

Clearing conditions:

When IRREC = 1, it is cleared by writing 0

1

Setting conditions:

When the asynchronous event counter value overflows

0

Clearing conditions:

When IRRTC = 1, it is cleared by writing 0

1

Setting conditions:

When the timer C counter value overflows

(from H'FF to H'00) or underflows (from H'00 to H'FF)