104

5.3.2

Clearing Standby Mode

Standby mode is cleared by an interrupt (IRQ

1

or IRQ

0

), WKP

7

to WKP

0

or by input at the

RES

pin.

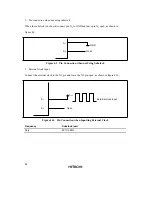

• Clearing by interrupt

When an interrupt is requested, the system clock pulse generator starts. After the time set in bits

STS2 to STS0 in SYSCR1 has elapsed, a stable system clock signal is supplied to the entire chip,

standby mode is cleared, and interrupt exception handling starts. Operation resumes in active

(high-speed) mode if MSON = 0 in SYSCR2, or active (medium-speed) mode if MSON = 1.

Standby mode is not cleared if the I bit of CCR is set to 1 or the particular interrupt is disabled in

the interrupt enable register.

• Clearing by

RES

input

When the

RES

pin goes low, the system clock pulse generator starts. After the pulse generator

output has stabilized, if the

RES

pin is driven high, the CPU starts reset exception handling. Since

system clock signals are supplied to the entire chip as soon as the system clock pulse generator

starts functioning, the

RES

pin should be kept at the low level until the pulse generator output

stabilizes.