106

5.3.4

Standby Mode Transition and Pin States

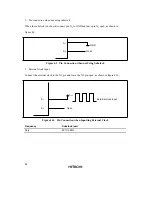

When a SLEEP instruction is executed in active (high-speed) mode or active (medium-speed)

mode while bit SSBY is set to 1 and bit LSON is cleared to 0 in SYSCR1, and bit TMA3 is

cleared to 0 in TMA, a transition is made to standby mode. At the same time, pins go to the high-

impedance state (except pins for which the pull-up MOS is designated as on). Figure 5.2 shows

the timing in this case.

SLEEP instruction fetch

Internal data bus

Fetch of next instruction

Port output

Pins

High-impedance

Active (high-speed) mode or active (medium-speed) mode

Standby mode

SLEEP instruction execution

Internal processing

ø

Figure 5.2 Standby Mode Transition and Pin States

5.3.5

Notes on External Input Signal Changes before/after Standby Mode

1. When external input signal changes before/after standby mode or watch mode

When an external input signal such as

IRQ

or

WKP

is input, both the high- and low-level

widths of the signal must be at least two cycles of system clock ø or subclock øSUB (referred

to together in this section as the internal clock). As the internal clock stops in standby mode

and watch mode, the width of external input signals requires careful attention when a transition

is made via these operating modes. Ensure that external input signals conform to the conditions

stated in 3, Recommended timing of external input signals, below

2. When external input signals cannot be captured because internal clock stops

The case of falling edge capture is illustrated in figure 5.3

As shown in the case marked "Capture not possible," when an external input signal falls

immediately after a transition to active (high-speed or medium-speed) mode or subactive

mode, after oscillation is started by an interrupt via a different signal, the external input signal

cannot be captured if the high-level width at that point is less than 2 t

cyc

or 2 t

subcyc

.

3. Recommended timing of external input signals

To ensure dependable capture of an external input signal, high- and low-level signal widths of

at least 2 t

cyc

or 2 t

subcyc

are necessary before a transition is made to standby mode or watch

mode, as shown in "Capture possible: case 1."