223

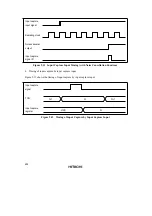

5. TGC clear timing

TCG can be cleared by the rising edge, falling edge, or both edges of the input capture input

signal.

Figure 9.13 shows the timing for clearing by both edges.

Input capture

input signal

Input capture

signal F

Input capture

signal R

TCG

N

N

H'00

H'00

Figure 9.13 TCG Clear Timing