322

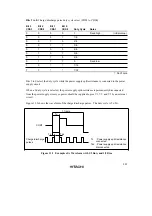

Start

Set A/D conversion speed

and input channels

Enable A/D conversion

end interrupt

Start A/D conversion

A/D conversion

end interrupt?

Yes

No

End

Yes

No

Clear bit IRRAD to

0 in IRR2

Read ADRRH/ADRRL data

Perform A/D

conversion?

Figure 12.5 Flow Chart of Procedure for Using A/D Converter (Interrupts Used)

12.6

Application Notes

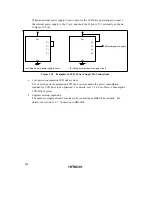

•

Data in ADRRH and ADRRL should be read only when the A/D start flag (ADSF) in the A/D

start register (ADSR) is cleared to 0.

•

Changing the digital input signal at an adjacent pin during A/D conversion may adversely

affect conversion accuracy.

•

When A/D conversion is started after clearing module standby mode, wait for 10 ø clock

cycles before starting.