MB95630H Series

40

FUJITSU SEMICONDUCTOR LIMITED

MN702-00009-1v0-E

CHAPTER 3 CLOCK CONTROLLER

3.4 Clock Modes

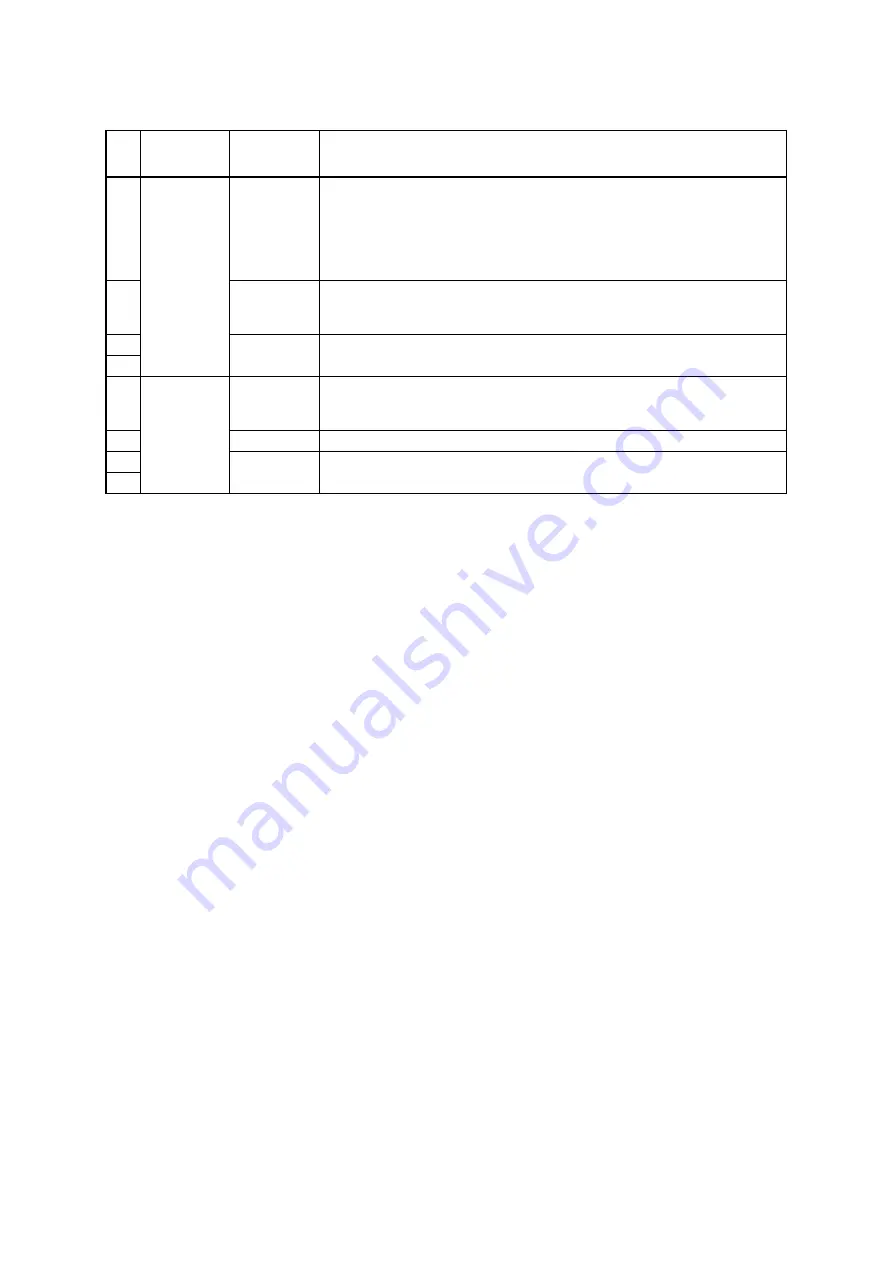

(13)

Sub-CR clock

Main CR clock/

Main CR PLL

clock

When the clock mode select bits in the system clock control register (SYCC:SCS[2:0])

are set to "0b110", the device transits to main CR clock mode after waiting for the

main CR clock oscillation stabilization wait time.

When the clock mode select bits in the system clock control register (SYCC:SCS[2:0])

are set to "0b111", the device transits to main CR PLL clock mode after waiting for the

main CR PLL clock oscillation stabilization wait time.

(14)

Main clock

When the clock mode select bits in the system clock control register (SYCC:SCS[2:0])

are set to "0b010", the device transits to main clock mode after waiting for the main

clock oscillation stabilization wait time.

(15)

Subclock

Same as (3) and (4)

(16)

(17)

Subclock

Main CR clock/

Main CR PLL

clock

Same as (13)

(18)

Main clock

Same as (14)

(19)

Sub-CR clock

Same as (1) and (2)

(20)

Table 3.4-1

Clock Mode State Transition Table (2 / 2)

Current

State

Next State

Description

Содержание MB95630H Series

Страница 2: ......

Страница 4: ......

Страница 8: ...iv ...

Страница 20: ...xvi ...

Страница 106: ...MB95630H Series 86 FUJITSU SEMICONDUCTOR LIMITED MN702 00009 1v0 E CHAPTER 6 I O PORT 6 2 Configuration and Operations ...

Страница 282: ...MB95630H Series 262 FUJITSU SEMICONDUCTOR LIMITED MN702 00009 1v0 E CHAPTER 14 LIN UART 14 8 Notes on Using LIN UART ...

Страница 642: ...MB95630H Series 622 FUJITSU SEMICONDUCTOR LIMITED MN702 00009 1v0 E APPENDIX A Instruction Overview A 5 Instruction Map ...

Страница 644: ......