S1C6S3N2 TECHNICAL HARDWARE

EPSON

I-97

CHAPTER 5: SUMMARY OF NOTES

SUMMARY OF NOTES

Notes for Low Current Consumption

The S1C6S3N2 Series contains control registers for each of

the circuits so that current consumption can be lowered.

These control registers lower the current consumption

through programs that operate the circuits at the minimum

levels.

The following text explains the circuits that can control

operation and their control registers. Refer to these when

putting programs together.

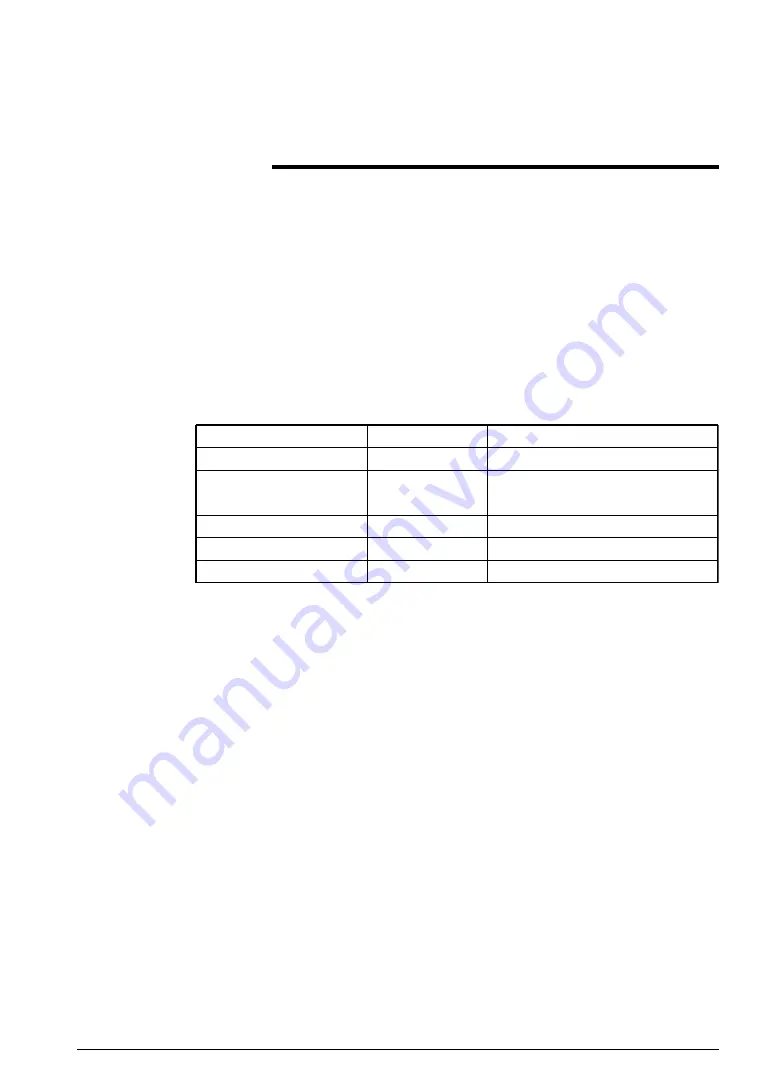

Table 5.1.1 Circuits and control registers

CHAPTER 5

5.1

Below are the circuit statuses at initial reset.

CPU:

Operating status

CPU operating frequency:

Low speed side (CLKCHG = "0"),

OSC3 oscillation circuit stop

status (OSCC = "0")

Heavy load protection mode: Normal operating mode

(HLMOD = "0")

SVD circuit:

OFF status (HLMOD = "0", BLS = "0")

Analog comparator:

OFF status (AMPON = "0")

Also, be careful about panel selection because the current

consumption can differ by the order of several µA on ac-

count of the LCD panel characteristics.

Circuits (and Items)

CPU

CPU operation frequency

(S1C6S3A2)

Heavy load protection mode

SVD circuit

Analog comparator

Control Registers

HALT instruction

CLKCHG, OSCC

HLMOD

HLMOD, BLS

AMPON

Order of Consumed Current

See electrical characteristics (Chapter 7)

See electrical characteristics (Chapter 7)

See electrical characteristics (Chapter 7)

Severral tens

µ

A

Severral tens

µ

A

Содержание S1C6S3N2

Страница 4: ......

Страница 6: ......

Страница 7: ...Hardware Hardware S1C6S3N2 I Technical Hardware ...

Страница 8: ......

Страница 141: ...Software Software S1C6S3N2 II Technical Software ...

Страница 142: ......

Страница 146: ......