18 UNIVERSAL SERIAL INTERFACE (USI)

S1C33L26 TECHNICAL MANUAL

Seiko Epson Corporation

18-15

(5) Generating repeated start condition

The procedure is the same as that of data transmission in I

2

C master mode.

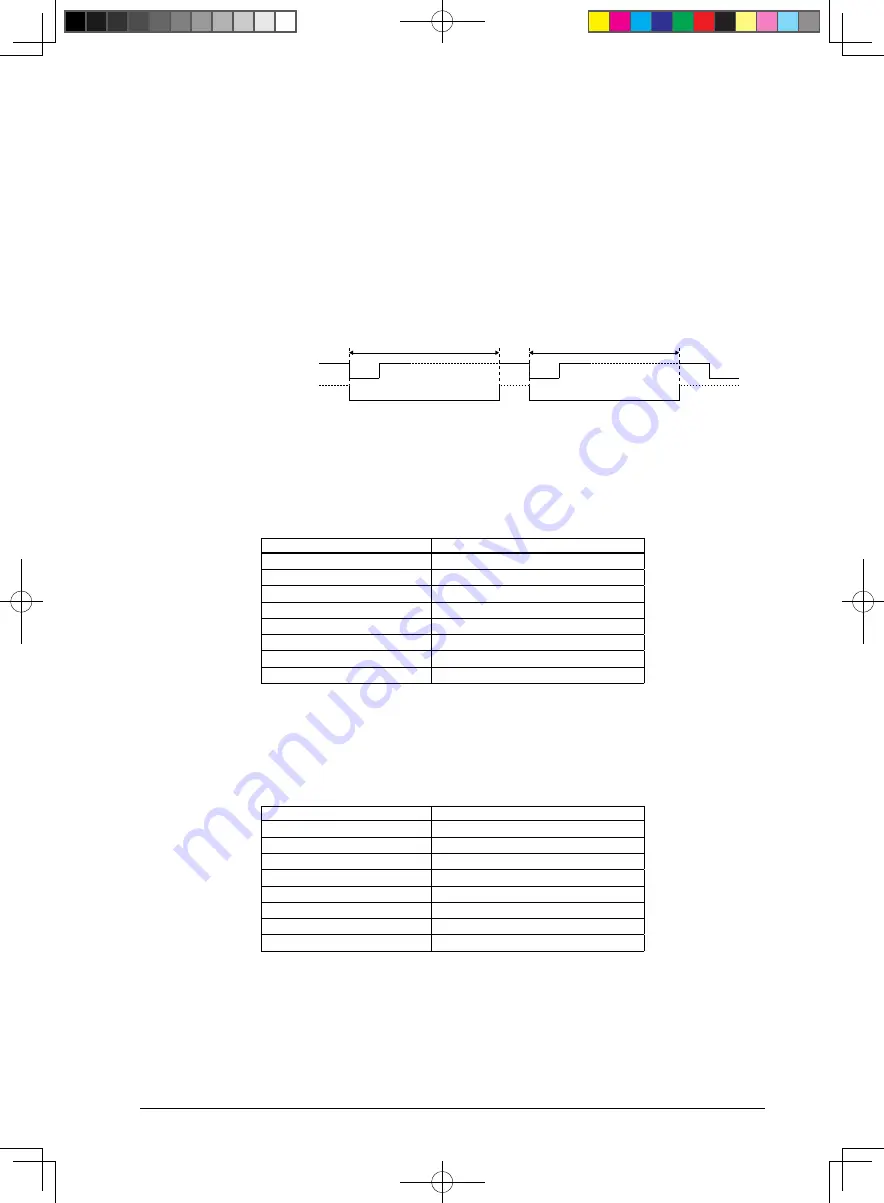

Clock stretch function

During transmitting/receiving data, the slave device may issue a wait request to the master device by pulling

down the SCL line to low until the slave device becomes ready to transmit/receive the subsequent data. The

master device enters a standby state until the wait request is canceled (the SCL line goes high).

This I

2

C controller supports this clock stretch function. When a clock stretch condition is detected after a slave

address or data has been sent/received, this module enters a waiting status and it does not start operating even if

it accepts a trigger for data transfer until the clock stretch status is canceled. IMBSY is maintained at 1 until the

triggered operation has completed including a waiting status.

USI_CK pin (master output)

USI_CK pin (slave output)

Clock stretch

Clock stretch

5.3.10 Clock Stretch

Figure 18.

Control method in I

2

C slave mode

Data transfer in I

2

C slave mode is controlled using ISTGMOD[2:0]/USI_ISTG register and ISTG/USI_ISTG

register. Select an I

2

C slave operation using ISTGMOD[2:0] and write 1 to ISTG as the trigger. The I

2

C con-

troller controls the I

2

C bus to generate the specified operating status.

5.3.3 Trigger List in I

Table 18.

2

C Slave Mode

ISTGMOD[2:0]

Trigger

0x7

Reserved

0x6

ACK/NAK reception

0x5

NAK transmission

0x4

ACK transmission

0x3

Data reception/stop condition detection

0x2

Data transmission

0x1

Reserved

0x0

Wait for start condition

(Default: 0x0)

Writing 1 to ISTG sets ISBSY/USI_ISIF register to 1 indicating that the I

2

C controller is busy (operating).

When the specified operation has finished, ISBSY is reset to 0. At the same time, the interrupt flag (ISIF/USI_

ISIF register) is also set to 1. After an interrupt occurs, read the status bits (ISSTA[2:0]/USI_ISIF register) to

check the operation finished. Then, clear ISIF by writing 1. This also automatically reset ISSTA[2:0] to 0x0.

5.3.4 I

Table 18.

2

C Slave Status Bits

ISSTA[2:0]

Status

0x7

Reserved

0x6

NAK has been received.

0x5

ACK has been received.

0x4

ACK or NAK has been sent.

0x3

End of receive data.

0x2

End of transmit data.

0x1

Stop condition has been detected.

0x0

Start condition has been detected.

(Default: 0x0)