ADV8005 Hardware Reference Manual

UG-707

1.3.

PROTOCOL FOR MAIN I

2

C PORT

The system controller initiates a data transfer by establishing a start condition, defined by a high to low transition on SDA while SCL remains

high. This transition indicates that an address/data stream will follow. All peripherals respond to the start condition and shift the next eight bits

(7-bit address and R/W bit). The bits are transferred from MSB down to LSB. The peripheral that recognizes the transmitted address responds

by pulling the data line low during the ninth clock pulse. This is known as an acknowledge bit. All other devices withdraw from the bus at this

point and maintain an idle condition.

In the idle condition, the device monitors the SDA and SCL lines for the start condition and the correct transmitted address. The R/W bit

determines the direction of the data. A logic 0 on the LSB of the first byte means that the master will write information to the peripheral. A logic

1 on the LSB of the first byte means that the master will read information from the peripheral.

The

has a single 8-bit I

2

C slave address. All register maps within the

can be accessed through this I

2

C address through 16-

bit addressing and 8-bit data registers. The

acts as a standard slave device on the I

2

C bus. It interprets the first byte as the I

2

C address

and the second byte and third bytes as the appropriate subaddress. The fourth byte is then considered the data for this subaddress register. This

means that I

2

C writes to the part will be in the form <I

2

C Address>, <Address MSBs>, <Address LSBs>, <Data>.

For example, to write 0xFF to the encoder register map, register 0x59AF, the I

2

C writes needed are 0x1A, 0x59, 0xAF, 0xFF. The addresses are

outlined in

shows the register map architecture for the

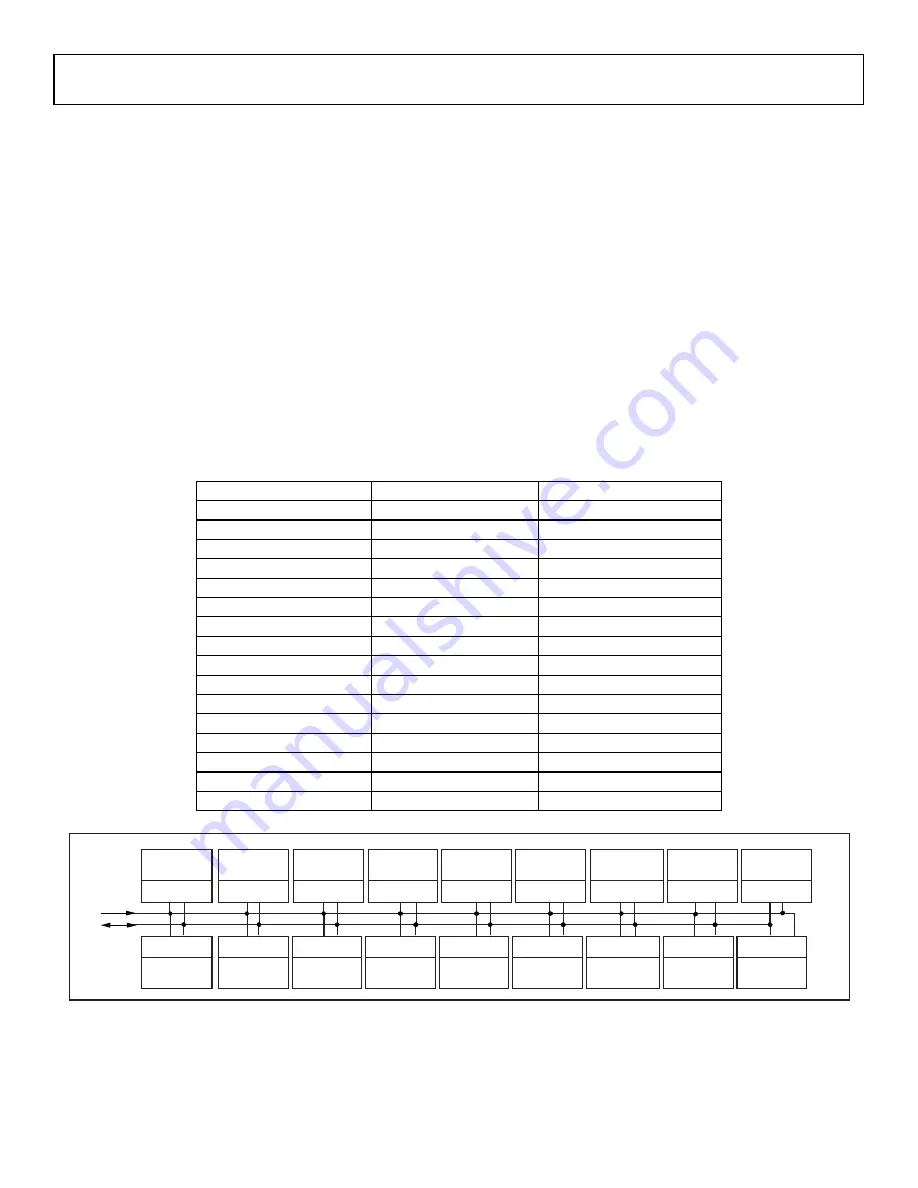

Table 2:

2

C Address and Register Address Range for Different HW Blocks

Register Map Name

I

2

C Address

Register Address

IO Map

0x1A (0x18 with LSB low)

0x1A00 to 0x1BFF

Primary VSP Map

0xE800 to 0xE8FF

Primary VSP Map 2

0xE900 to 0xE9FF

Secondary VSP Map

0xE600 to 0xE6FF

Rx Main Map

0xE200 to 0xE2FF

Rx InfoFrame Map

0xE300 to 0xE3FF

Tx1 Main Map

0xEC00 to 0xECFF

Tx1 EDID Map

0xEE00 to 0xEEFF

Tx1 UDP Map

0xF200 to 0xF2FF

Tx1 Test Map

0xF300 to 0xF3FF

Tx2 Main Map

0xF400 to 0xF4FF

Tx2 EDID Map

0xF600 to 0xF6FF

Tx2 UDP Map

0xFA00 to 0xFAFF

Tx2 Test Map

0xFB00 to 0xFBFF

Encoder Map

0xE400 to 0xE4FF

DPLL Map

0xE000 to 0xE0FF

Figure 7: Register Map Architecture

It is possible to use the subaddresses auto-increment feature, which allows data to be accessed from the starting subaddress. A data transfer is

always terminated by a stop condition. The user can also access any unique subaddress register on a one-by-one basis without having to update

all the registers.

IO

MAP

0x1A00 TO

0x1BFF

0xE800 TO

0xE8FF

0xE600 TO

0xE6FF

DPLL

MAP

0xE000 TO

0xE0FF

Rx MAIN

MAP

0xE200 TO

0xE2FF

Rx INFOFRAME

MAP

0xE300 TO

0xE3FF

ENCODER

MAP

0xE400 TO

0xE4FF

Tx1 TEST

MAP

0xF300 TO

0xF3FF

Tx1 MAIN

MAP

Tx1 EDID

MAP

Tx1 CEC

MAP

Tx1 UDP

MAP

Tx2 MAIN

MAP

Tx2 EDID

MAP

Tx2 CEC

MAP

Tx2 UDP

MAP

Tx2 TEST

MAP

0xEC00 TO

0xECFF

0xEE00 TO

0xEEFF

0xF000 TO

0xF0FF

0xF200 TO

0xF2FF

0xF400 TO

0xF4FF

0xF600 TO

0xF6FF

0xF800 TO

0xF8FF

0xFA00 TO

0xFAFF

0xFB00 TO

0xFBFF

I

2

C

ADDRESS

0x18/0x1A

SCL

SDA

09803-021

PRIMARY VSP

MAP

SECONDARY

VSP MAP

0xE900 TO

0xE9FF

PRIMARY VSP

MAP 2

Rev. A | Page 23 of 317