Chapter 6 Deployment of the CPU 821xDP

CPU ADAM 821x

6-4

ADAM 8000 Manual CPU 821x – Rev 1.1

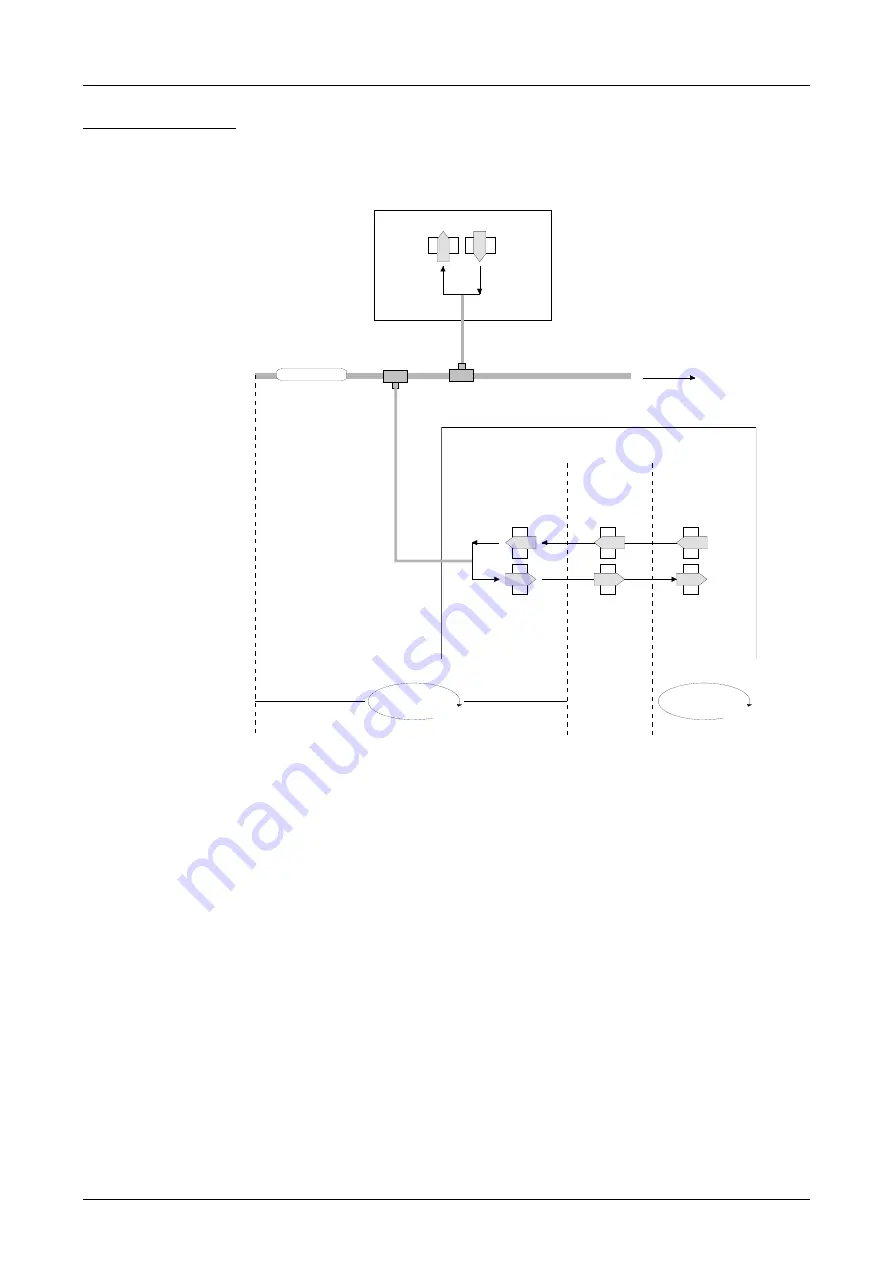

The data exchange between the DP master and the DP slave is performed

in a cycle using send and receive buffers.

DP-Master

Input

Output

CPU 821x DP with I/O-Modules

I/O Modules

Communications

Processor

buffer receive

Profibus DP

V-Bus

buffer send

V-Bus-Zyklus

DP-Zyklus

PE

PA

PE: Process picture of the inputs

PA: Process picture of the outputs

In one V-bus cycle (i.e. backplane bus) all input data of the single modules

are collected in the PE and all output data from the PA are transferred to

the output modules. After the data exchange is completed, the PE is

transferred to the sending buffer (buffer send) and the content of the input

buffer (buffer receive) is transferred to PA.

In one Profibus cycle the master contacts all its slaves with a data ex-

change. There the memory areas assigned to the Profibus are written resp.

read.

Afterwards the DP master transmits data of the input area to the receive

buffer of the communication processor and the data of the send buffer is

transferred into the Profibus output area.

The DP master to DP slave data exchange on the bus is repeated cyclically

and does not depend on the V-bus cycle.

The principle of

data transfer

operations

V-bus cycle

DP cycle