148

Chapter 4

0x32

Program the Egress port timings

PEI

chipset/MRC

0x33

Program the Memory IO registers

PEI

chipset/MRC

0x34

Perform steps required before JEDEC

PEI

chipset/MRC

0x35

Perform JEDEC memory initialization for all memory

rows

PEI

chipset/MRC

0x36

Setup DRAM control register for normal operation

and enable

PEI

chipset/MRC

0x37

Do ZQ calibration for DDR3

PEI

chipset/MRC

0x38

Perform final Dra/Drb programming, Set the mode of

operation for the memory channels

PEI

chipset/MRC

0x39

Set Enhanced addressing mode for each channel

PEI

chipset/MRC

0x40

Perform steps required after JEDEC init

PEI

chipset/MRC

0x41

Program the receive enable reference timing control

register

PEI

chipset/MRC

0x42

Post receive enable initialization

PEI

chipset/MRC

0x43

Enable sense amps. Reset read/write DQS pointers

PEI

chipset/MRC

0x44

Perform ME steps

PEI

chipset/MRC

0x45

Clear DRAM initialization bit in the ICH.

PEI

chipset/MRC

0x46

Program Thermal Management

PEI

chipset/MRC

0x47

Program TS on DIMM

PEI

chipset/MRC

0x48

Program TS on Board

PEI

chipset/MRC

0xAF

Exit MRC

PEI

chipset/MRC

0xE0

#define MEM_ERR_BAD_DIMM (S11)

PEI

chipset/MRC

0xE1

#define MEM_ERR_ECC_DIMM (S06)

PEI

chipset/MRC

0xE2

#define MEM_ERR_SIDES (S07)

PEI

chipset/MRC

0xE3

#define MEM_ERR_WIDTH (S08, S10)

PEI

chipset/MRC

0xE4

#define MEM_ERR_TRFC (FindTrasTrpTrcd)

PEI

chipset/MRC

0xE5

#define MEM_ERR_CAS_LATENCY (S12, S13)

PEI

chipset/MRC

0xE6

#define MEM_ERR_REFRESH (ProgDrt)

PEI

chipset/MRC

0xE7

#define MEM_ERR_BL8 (S14)

PEI

chipset/MRC

0xE9

#define MEM_ERR_FREQUENCY (findTCLTacTClk,

S13, S12, ProgramGraphicsFrequency,

ProgMchOdt, GetPlatformData)

PEI

chipset/MRC

0xEA

#define MEM_ERR_SIZE (S14)

PEI

chipset/MRC

0xEC

#define MEM_ERR_TRAS (FindTrasTrpTrcd)

PEI

chipset/MRC

0xED

#define MEM_ERR_TRP (FindTrasTrpTrcd)

PEI

chipset/MRC

0xEE

#define MEM_ERR_TRCD (FindTrasTrpTrcd)

PEI

chipset/MRC

0xEF

#define MEM_ERR_TWR (FindTrasTrpTrcd)

PEI

chipset/MRC

0xF0

#define MEM_ERR_RCVEN_FINDLOW

(CalibrateRcvenForGroup)

PEI

chipset/MRC

0xF1

#define MEM_ERR_RCVEN_FINDEDGE

(CalibrateRcvenForGroup)

PEI

chipset/MRC

0xF2

#define MEM_ERR_RCVEN_FINDPREAMBLE

(CalibrateRcvenForGroup)

PEI

chipset/MRC

0xF6

#define MEM_ERR_RCVEN_PREAMBLEEDGE

(CalibrateRcvenForGroup)

PEI

chipset/MRC

POST Code

Function

Phase

Component

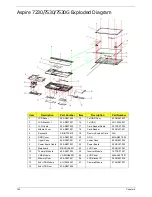

Содержание Aspire 7230

Страница 6: ...VI ...

Страница 10: ...X Table of Contents ...

Страница 54: ...44 Chapter 2 3 Reboot the system and key in the selected string qjjg9vy 07yqmjd etc for the BIOS user password ...

Страница 85: ...Chapter 3 75 5 Remove the bracket from the board 6 Remove the Finger Print Reader board from the Upper Cover ...

Страница 92: ...82 Chapter 3 4 Grasp the Subwoofer Module and lift it up to remove ...

Страница 94: ...84 Chapter 3 4 Lift the ExpressCard module away from the upper cover ...

Страница 101: ...Chapter 3 91 4 Lift up the bezel and remove it from the LCD Module ...

Страница 105: ...Chapter 3 95 5 Grasp the panel by both ends and lift to remove ...

Страница 107: ...Chapter 3 97 4 Remove the LCD brackets by pulling away from the LCD Panel as shown ...

Страница 110: ...100 Chapter 3 8 Connect the left and right Inverter cables 9 Connect the camera cable ...

Страница 113: ...Chapter 3 103 3 Tighten the four 4 captive screws on the heatsink 4 Connect the Fan cable to the Mainboard ...

Страница 118: ...108 Chapter 3 4 Connect the two FFC cables as shown 5 Connect the cable as shown ...

Страница 206: ...196 Appendix C ...