TPMC533 User Manual Issue 1.0.1

Page 72 of 107

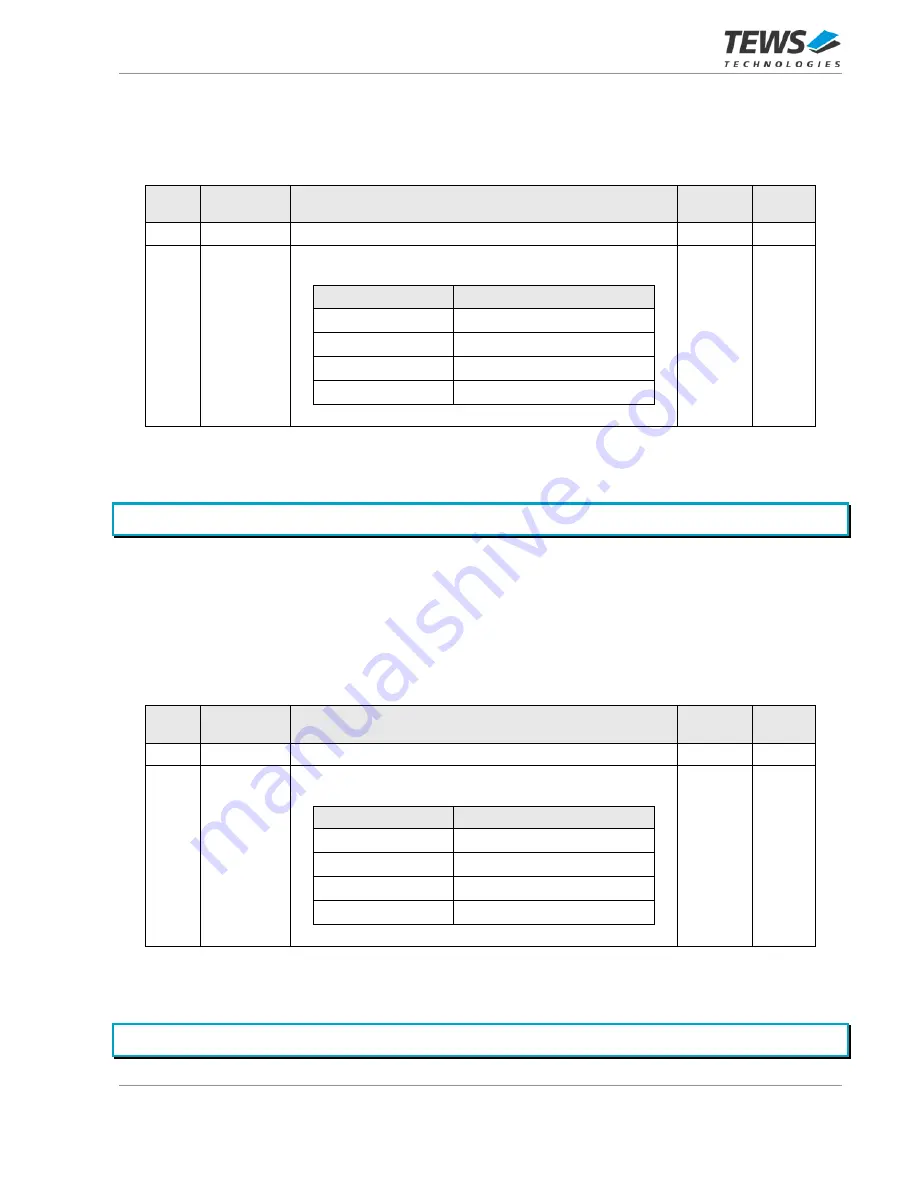

3.2.1.10.2 DIO Pull Resistors Register (0x39C)

All of the 8 Digital I/Os are connected to 4.7

kΩ pull resistor

s. The voltage, the pull resistors are connected to,

is programmable and can be configured to 3.3V, 5V, GND or floating level.

Bit

Symbol

Description

Access

Reset

Value

31:2

-

Reserved

-

-

1:0

VPULL_DIO

Digital I/O Pull Resistor Configuration

VPULL_DIO

Pull Resistor Configuration

00

Floating

01

Pull-Ups to +5V

10

Pull-Ups to +3.3V

11

Pull-Downs to GND

R/W

00

Table 3-70: DIO Pull Resistor Register

Note that the default configuration for the Digital I/O Pull Resistors is floating.

3.2.1.10.3 P14 Back I/O Pull Resistors Register (0x3A0)

All P14 Back I/O Signals (Global Conversion Clock 1, Global Conversion Clock 2 and Global Frame Trigger)

are connected to 4.7

kΩ pull resistor

s. The voltage, the pull resistors are connected to, is programmable and

can be configured to 3.3V, 5V, GND or floating level.

Bit

Symbol

Description

Access

Reset

Value

31:2

-

Reserved

-

-

1:0

VPULL_P14

P14 Back I/O Pull Resistor Configuration

VPULL_P14

Pull Resistor Configuration

00

Floating

01

Pull-Ups to +5V

10

Pull-Ups to +3.3V

11

Pull-Downs to GND

R/W

00

Table 3-71: P14 Back I/O Pull Resistor Register

Note that the default configuration for the P14 Back I/O Pull Resistors is floating.