TPMC533 User Manual Issue 1.0.1

Page 20 of 107

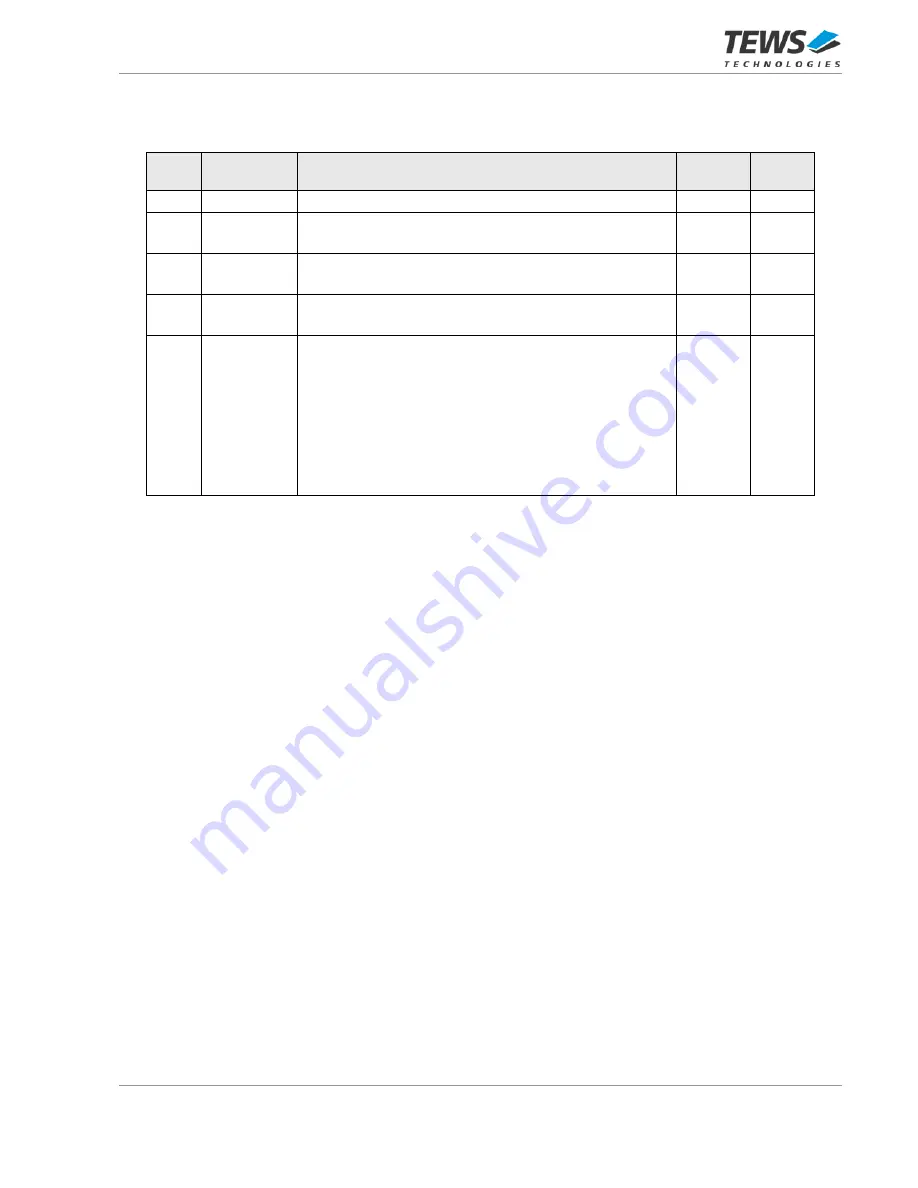

3.2.1.1.2

Global ADC Status Register (0x004)

For each ADC (for all eight ADC Channels of each ADC) on-board the TPMC533, status information can be

read from this read-only register.

Bit

Symbol

Description

Access

Reset

Value

31:4

-

Reserved

-

-

3

ADC4_BUSY

ADC4 Busy

Refer to the ADC1 Busy bit for description.

R

0

2

ADC3_BUSY

ADC3 Busy

Refer to the ADC1 Busy bit for description.

R

0

1

ADC2_BUSY

ADC2 Busy

Refer to the ADC1 Busy bit for description.

R

0

0

ADC1_BUSY

ADC1 Busy

Set when

•

analog sampling is in progress

•

data is transferred from the ADC

If ADC1 Operating Mode is set to "Manual Mode" in the

corresponding ADC Mode Register, this bit is set by writing

to ADC1_CONV_REQ in the Global ADC Control Register.

This bit must be read as '0' before data can be read from the

corresponding ADC Data Register.

R

0

Table 3-6 : Global ADC Status Register