TPMC533 User Manual Issue 1.0.1

Page 52 of 107

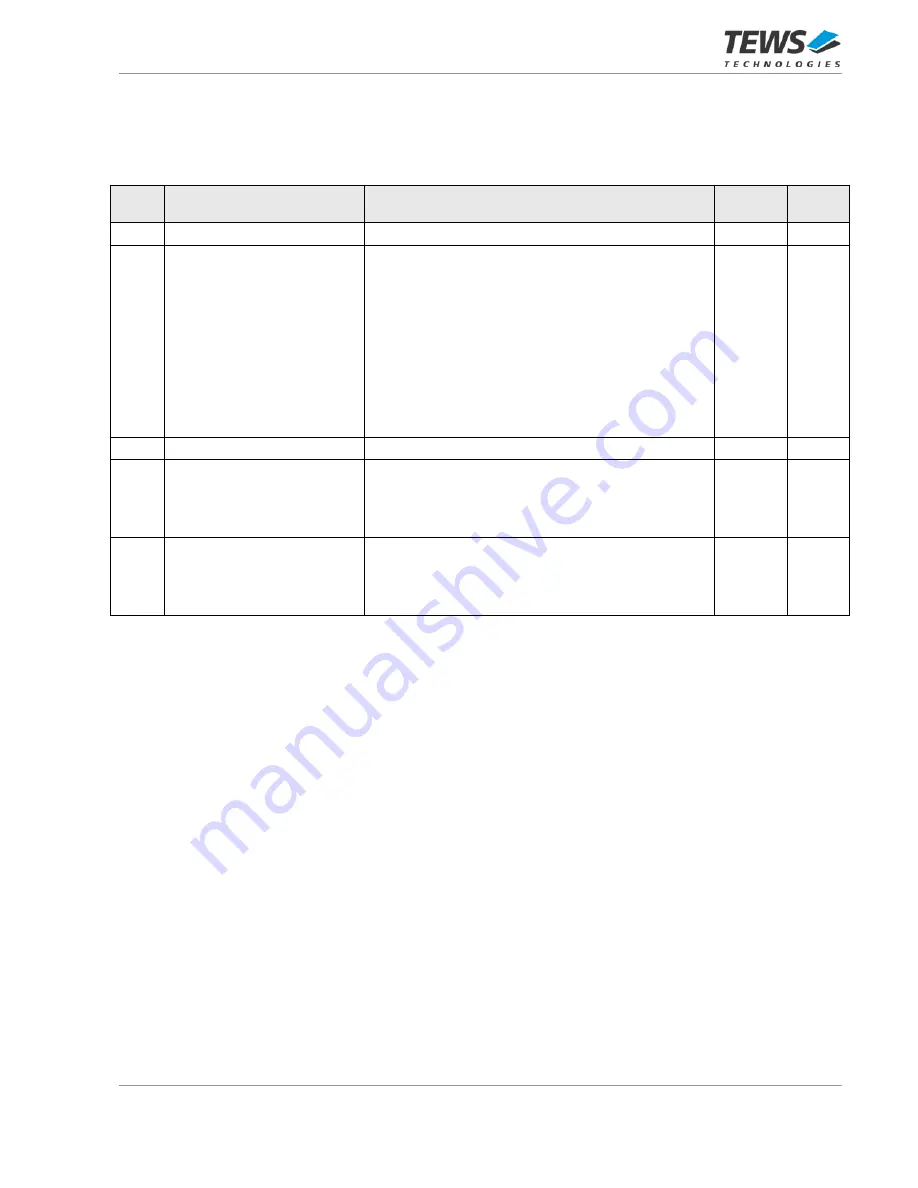

3.2.1.7.5

Conversion Signals Generator Enable Register (0x33C)

This register can be used for a synchronized start of the two Conversion Clocks and the Frame Trigger

generated on-board.

Bit

Symbol

Description

Access

Reset

Value

31:9

-

Reserved

-

-

8

FRAME_TRIG_GEN_ENA

Frame Trigger Generation Enable

0: Frame Trigger Generation Disabled

1: Frame Trigger Generation Enabled

If enabled, the configured Number of Frame Triggers to

be generated (Frame Trigger Generator Register 2) is

generated, starting with the next rising edge of the

associated Conversion Clock Generator output.

The Frame Trigger is output at the configured Frame

Trigger frequency but, of course, requires a running

Conversion Clock Generator Clock Source signal.

If disabled, the Frame Trigger output is ‘1’.

R/W

0

7:2

-

Reserved

-

-

1

CLK2_GEN_ENA

Conversion Clock 2 Generation Enable

0: Conversion Clock 2 Generation Disabled

1: Conversion Clock 2 Generation Enabled

If disabled, the clock output is ‘1’.

R/W

0

0

CLK1_GEN_ENA

Conversion Clock 1 Generation Enable

0: Conversion Clock 1 Generation Disabled

1: Conversion Clock 1 Generation Enabled

If disabled, the clock output is ‘1’.

R/W

0

Table 3-54: Conversion Signals Generator Enable Register