TPMC533 User Manual Issue 1.0.1

Page 45 of 107

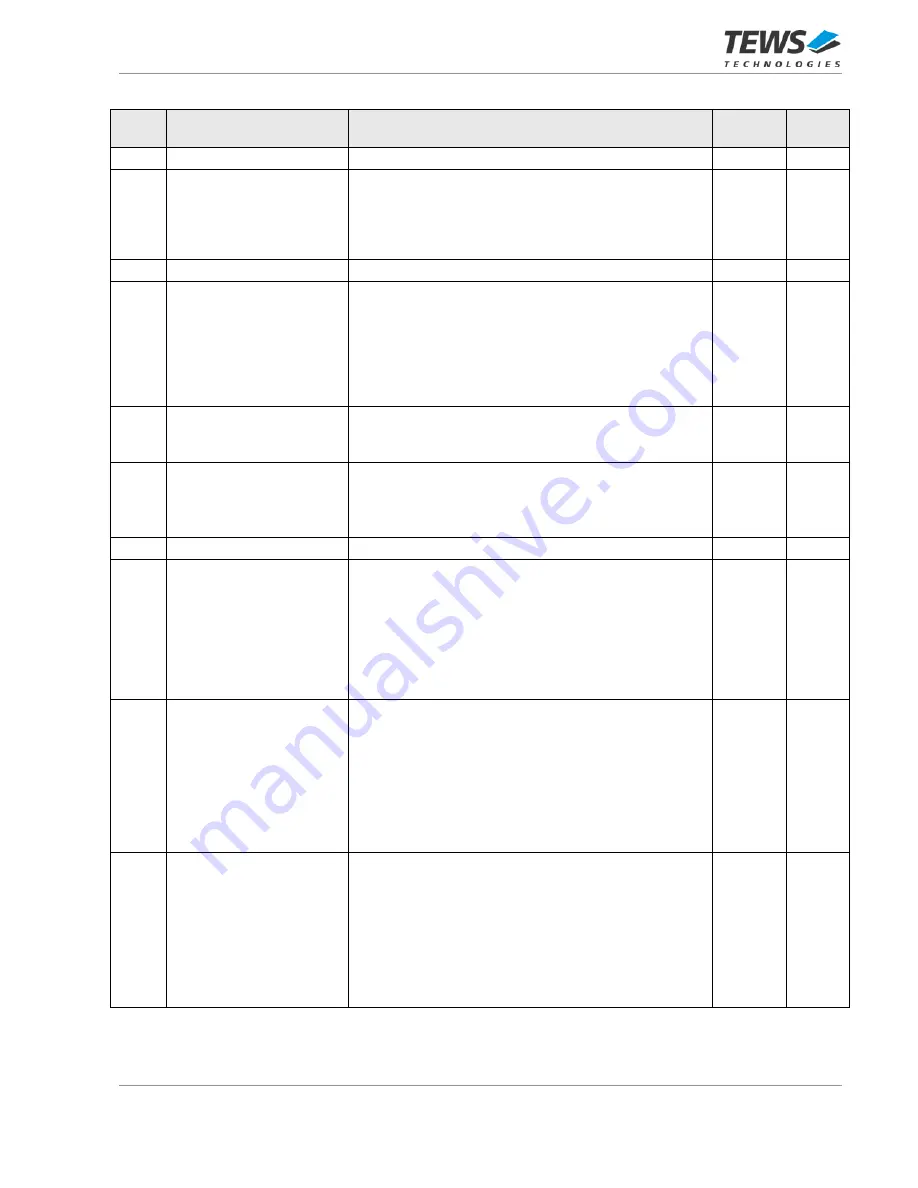

3.2.1.6.2

DAC Sequencer Status Register (0x2EC)

Bit

Symbol

Description

Access

Reset

Value

31:21

-

Reserved

-

-

20

RD_DMA_TERM

DMA Buffer Termination

The end of the DMA Buffer was reached (all values have

been read out of the DMA Buffer and written to the FIFO).

This bit is automatically cleared when a new DMA Buffer

is provided by writing to the DMA Buffer Length Register.

R

0

19

-

Reserved

-

-

18

RD_DMA_ERR

DMA Error

A PCI Master Abort occurred because the addressed PCI

Target did not respond or a PCI Target Abort occurred

because the addressed PCI Target detected a fatal error.

In case of an error, the DMA Controller operation is

automatically stopped.

This bit is cleared when the DMA Controller is disabled.

R

0

17

RD_DMA_BUSY

DMA Busy

Indicates that the DMA Controller is currently busy

(active).

R

0

16

RD_DMA_IDLE

DMA Idle

Indicates that the DMA Controller is currently in Idle State.

A DMA transfer may be started (a DMA buffer may be

provided) by writing to the DMA Buffer Length Register.

R

0

15:7

-

Reserved

-

-

6

OU_FRAME_ERR

Output Unit Frame Error

A Frame Trigger event occurs, but the configured Number

of Conversions has not been processed so far.

In case of this error, the conversion process is terminated

(no more conversion pulses are generated) and the

Output Unit operation is stopped.

This bit is automatically cleared when the Output Unit is

disabled.

R

0

5

TIMING_ERR

Output Unit DAC Timing Error

The DAC Sequencer's Conversion Rate requests the next

conversion, but at least one of the involved DACs does

not allow a conversion at the moment because a serial

data transfer is about to start or has just been finished.

In case of this error, the conversion process is terminated

(no more conversion pulses are generated) and the

Output Unit operation is stopped. This bit is automatically

cleared when the Output Unit is disabled.

R

0

4

DATA_ERR

Output Unit Data Underrun Error

The DAC Sequencer's Conversion Rate requests the next

conversion, but not all DACs are properly pre-loaded with

data.

In case of this error, the conversion process is terminated

(no more conversion pulses are generated) and the

Output Unit operation is stopped.

This bit is automatically cleared when the Output Unit is

disabled.

R

0