TPMC533 User Manual Issue 1.0.1

Page 51 of 107

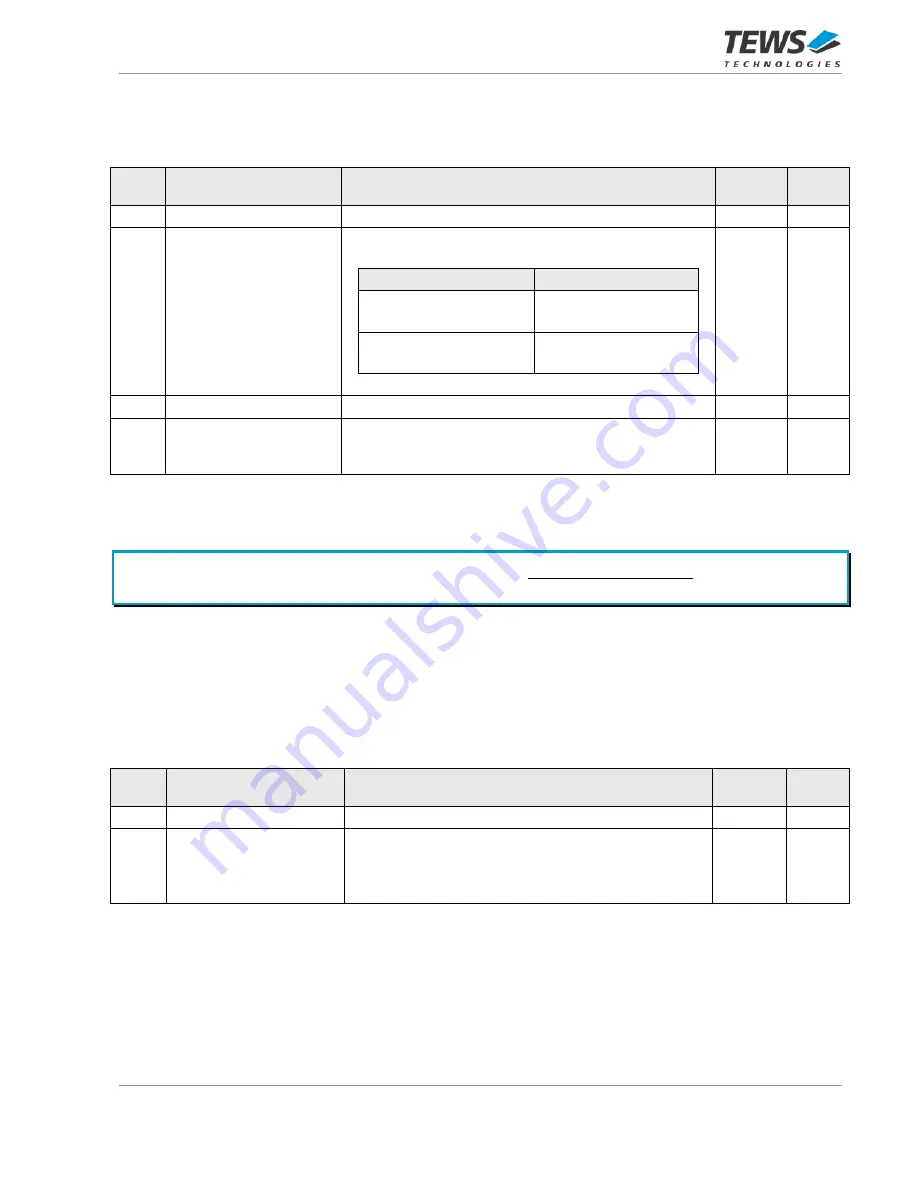

3.2.1.7.3

Frame Trigger Generator Register 1 (0x32C)

This register determines the frequency of the Frame Trigger Generator output (Frame Trigger Rate).

Bit

Symbol

Description

Access

Reset

Value

31:30

-

Reserved

-

-

29

FRAME_TRIG_GEN_SRC

Frame Trigger Generator Clock Source

FRAME_TRIG_GEN_SRC

Clock Source

0

Conversion Clock 1

Generator

1

Conversion Clock 2

Generator

R/W

0

28

-

Reserved

-

-

27:0

FRAME_TRIG_GEN_DIV

Frame Trigger Generator Divider

These bits set the divider for the selected Conversion Clock

Generator output.

R/W

0xFFF

FFFF

Table 3-52: Frame Trigger Generator Register 1

The frequency of the Frame Trigger Generator output is:

FRAME_TRIG_GEN_SRC

FRAME_TRIG_1

3.2.1.7.4

Frame Trigger Generator Register 2 (0x330)

This register determines the number of Frame Triggers generated on-board.

Frame Trigger generation is started in the Conversion Signals Generator Enable Register.

Bit

Symbol

Description

Access

Reset

Value

31:28

-

Reserved

-

-

27:0

FRAME_TRIG_GEN_NUM

Number of Frame Triggers to be generated

Sets the number of Frame Triggers to be generated.

If set to '0', Frame Triggers are generated continuously at

the configured Frame Trigger frequency.

R/W

0x000

0000

Table 3-53: Frame Trigger Generator Register 2