TPMC533 User Manual Issue 1.0.1

Page 54 of 107

3.2.1.7.7

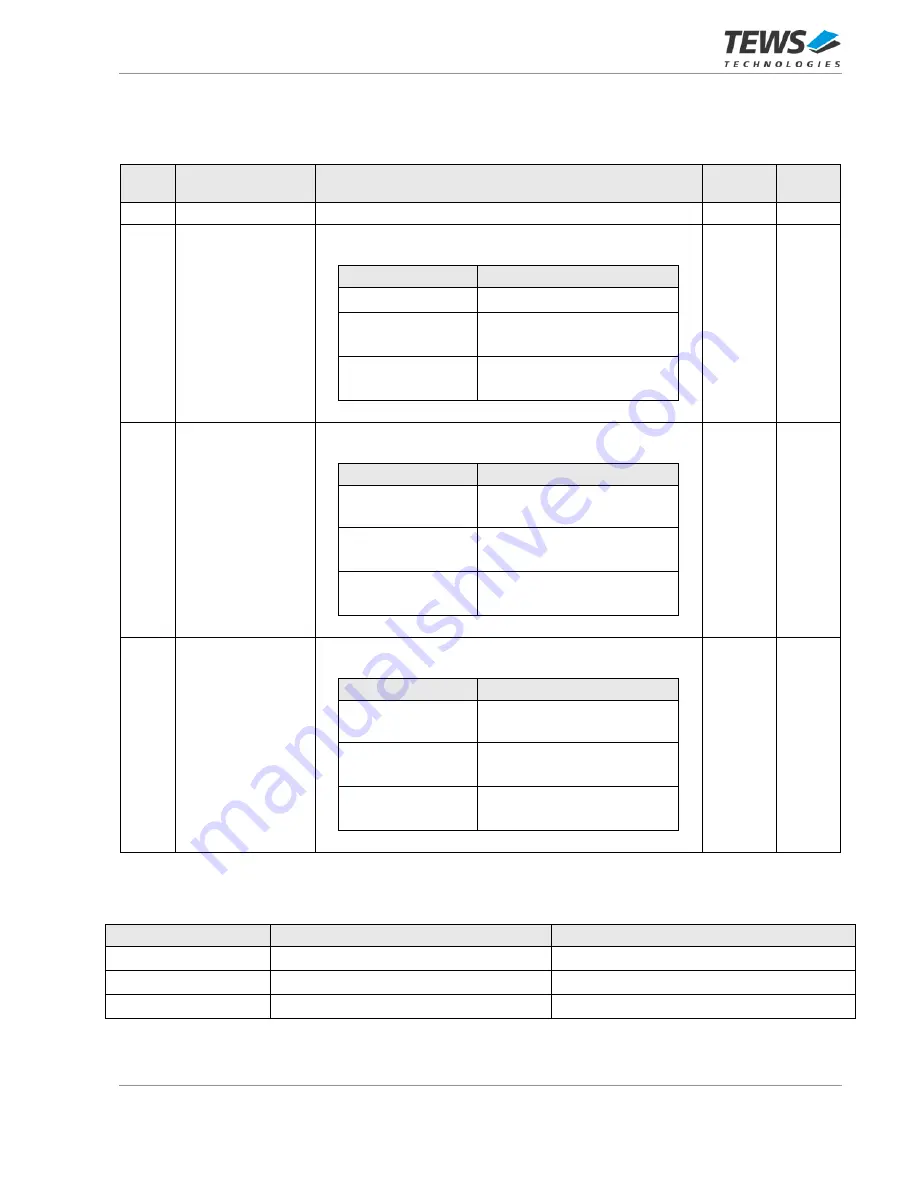

Conversion Signals Source Selection Register (0x344)

This register is used to select the signal source for the three Conversion Signals.

Bit

Symbol

Description

Access

Reset

Value

31:6

-

Reserved

-

-

5:4

FRAME_TRIG_SRC

Frame Trigger Source

FRAME_TRIG_SRC

Source

0x

Frame Trigger Generator

10

P14 Back I/O

Global Frame Trigger

11

Front I/O

Digital I/O 5

R/W

00

3:2

CLK2_SRC

Conversion Clock 2 Source

CLK2_SRC

Source

0x

Conversion Clock 2

Generator

10

P14 Back I/O

Global Conversion Clock 2

11

Front I/O

Digital I/O 3

R/W

00

1:0

CLK1_SRC

Conversion Clock 1 Source

CLK1_SRC

Source

0x

Conversion Clock 1

Generator

10

P14 Back I/O

Global Conversion Clock 1

11

Front I/O

Digital I/O 1

R/W

00

Table 3-56: Conversion Signals Source Selection Register

System Configuration

Conversion Signals Generator Output Driver

Conversion Signals Source Selection

Single Card

Output Driver disabled

Conversion Signal Generators

Multiboard Master Card

P14 Back I/O or Front I/O

P14 Back I/O or Front I/O

Multiboard Target Card

Output Driver disabled

P14 Back I/O or Front I/O