TPMC533 User Manual Issue 1.0.1

Page 29 of 107

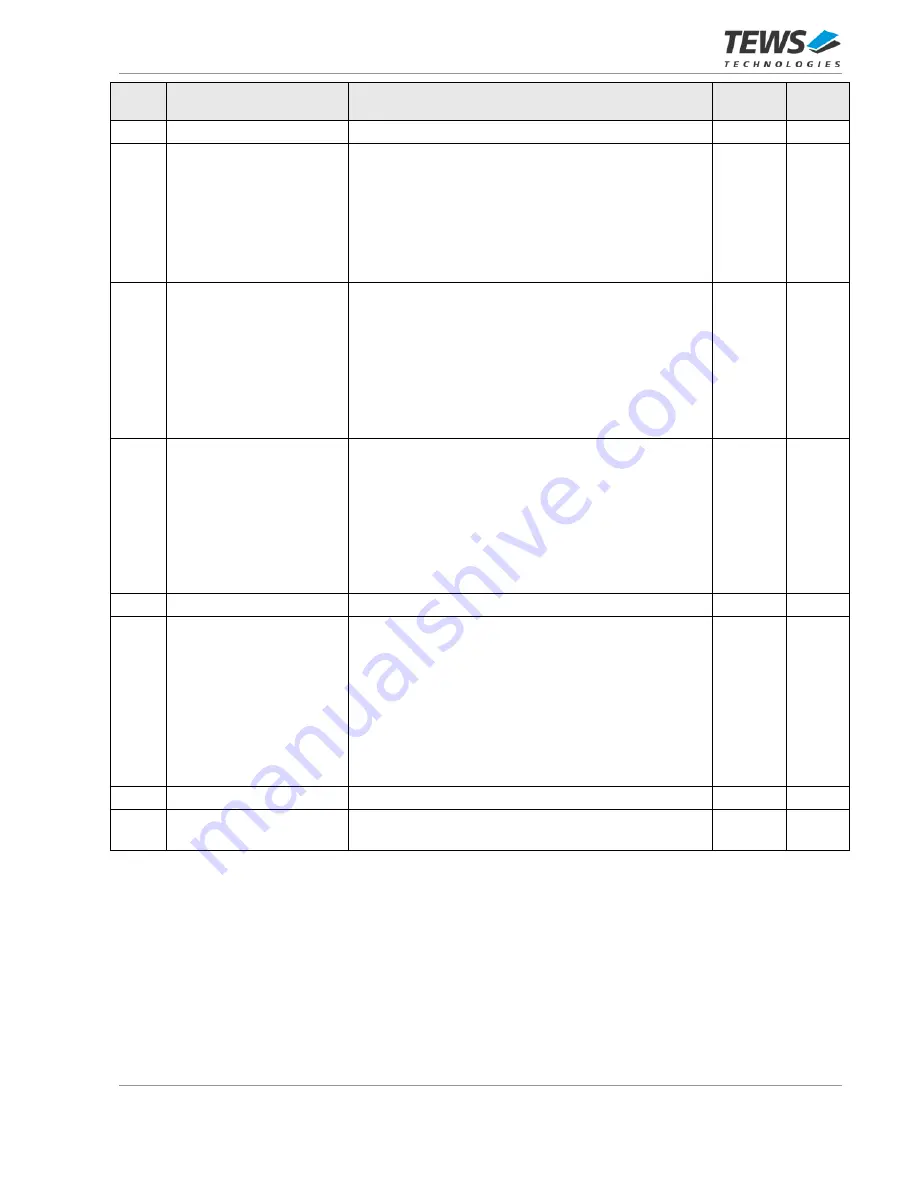

Bit

Symbol

Description

Access

Reset

Value

15:7

-

Reserved

-

-

6

IU_FRAME_ERR

Input Unit Frame Error

A Frame Trigger event occurs, but the configured Number

of Conversions has not been processed so far.

In case of this error, the conversion process is terminated

(no more conversion pulses are generated) and the Input

Unit operation is stopped.

This bit is automatically cleared when the Input Unit is

disabled.

R

0

5

CONV_ERR

Input Unit Conversion Error

The Sequencer Conversion Clock Source requests the

next conversion, but the ADCs are still busy performing

the conversion process of the previous conversion.

In case of this error, the conversion process is terminated

(no more conversion pulses are generated) and the Input

Unit operation is stopped.

This bit is automatically cleared when the Input Unit is

disabled.

R

0

4

FIFO_OF

Input Unit FIFO Overflow Error

The Input Unit wants to write sampled values from the

ADCs to the FIFO but the FIFO is full because AD

samples could not be written to Host RAM fast enough.

In case of this error, the conversion process is terminated

(no more conversion pulses are generated) and the Input

Unit operation is stopped.

This bit is automatically cleared when the Input Unit is

disabled.

R

0

3

-

Reserved

-

-

2

IU_CONV_ACTIVE

Input Unit Conversion Process Active

Indicates that the conversion process is active.

In Normal Mode, this bit is set when the software sets the

Input Unit Start Conversion bit. This bit is cleared when

the configured Number of Conversions has been

performed.

In Frame Mode, this bit is set when a Frame Trigger starts

the conversion process (except in a frame error case).

This bit is cleared when the configured Number of

Conversions has been performed (for a single frame).

R

0

1

-

Reserved

-

-

0

IU_IDLE

Input Unit Idle

Indicates that the Input Unit is currently in Idle State.

R

0

Table 3-22: ADC Sequencer Status Register