TPMC533 User Manual Issue 1.0.1

Page 40 of 107

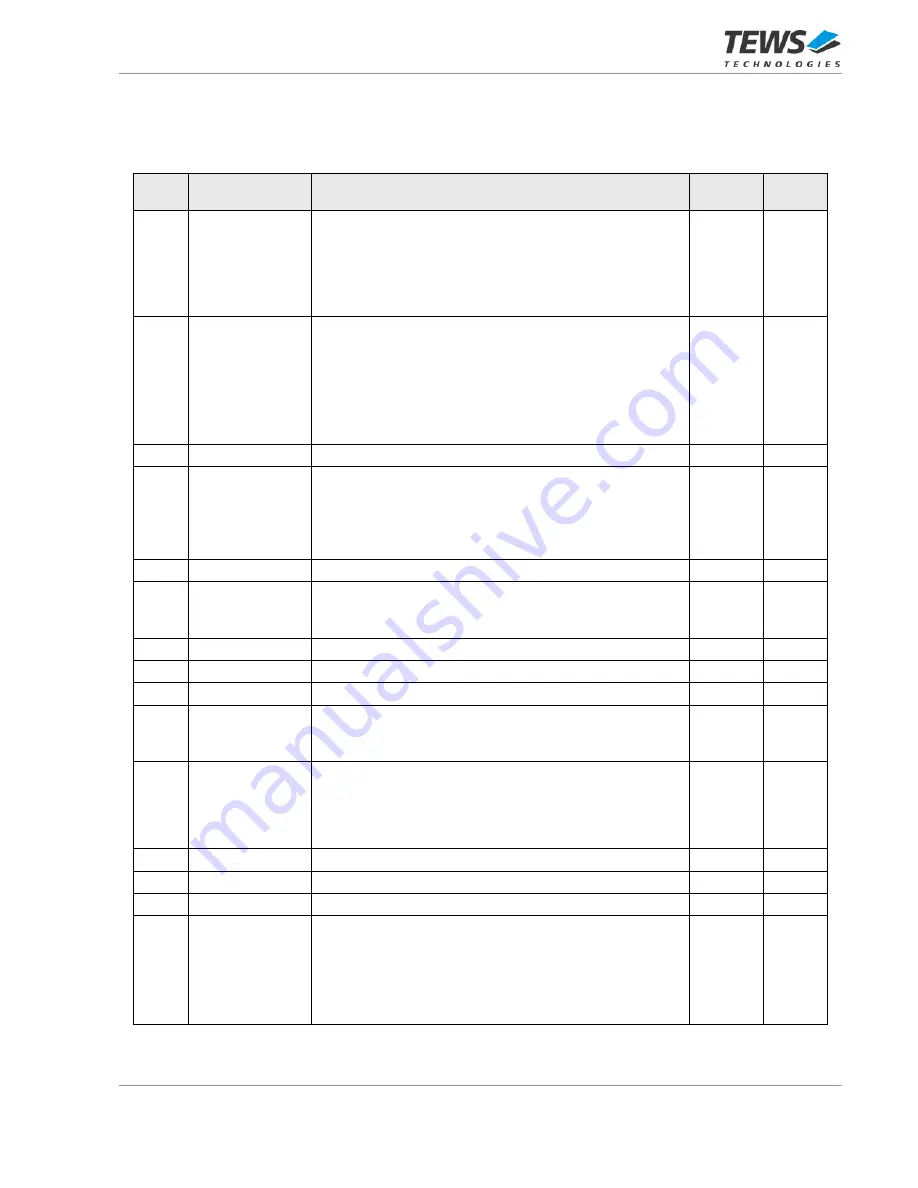

3.2.1.5.4

DAC Status Registers (0x188, 0x1B8, 0x1E8 and 0x218)

Each DAC device provides an internal status register, which is reflected in the corresponding DAC Status

Register. The DAC Status Register is updated when a status register read is requested by writing a ‘1’ to the

DACx_RDSTA bit.

Bit

Symbol

Description

Access

Reset

Value

31

DACx_RDSTA

Read DAC internal Status Register

When set, a request for reading the DAC status is logged

and the status valid bit (DACx_SVAL) is cleared. When the

DAC status read is done, the DAC Status Register is

updated and the DACx_SVAL bit is set again.

This bit clears immediately.

R/S

0

30

DACx_SVAL

Status is valid

0: Outdated Status Information

1: Updated Status Information

This bit indicates that the other register bits of the DAC

Status Register have been updated after a DAC status read.

The bit is cleared upon a DAC status read request

(DACx_RDSTA) or by writing a '1' to this bit.

R/C

0

29

-

Reserved

-

-

28

DACx_AUTOSTA

Automatic DAC internal Status Register Read

0: No Automatic DAC Status Read

1: Automatic DAC Status Read after each conversion

In automatic mode, the DAC Status is read automatically

after a DAC conversion.

R/W

0

27:10

-

Reserved

-

-

9

DACx_TSD

DAC Thermal Shutdown Alert

In the event of an over-temperature situation, the DAC is

powered down and this bit is set.

R

0

8

DACx_OCD

DAC Channel D Over-current Alert. See OCA description.

R

0

7

DACx_OCC

DAC Channel C Over-current Alert. See OCA description.

R

0

6

DACx_OCB

DAC Channel B Over-current Alert. See OCA description.

R

0

5

DACx_OCA

DAC Channel A Over-current Alert

In the event of an over-current situation on DAC channel A it

is powered down and this bit is set.

R

0

4

DACx_PUREF

DAC Reference Power-Up

When set, this bit indicates that the DAC internal reference

is powered-up. Since the DACs are operating with the

internal reference, this bit should always be set for any

status read from the DACs.

R

0

3

DACx_PUD

DAC Channel D Power-Up. See PUA description.

R

0

2

DACx_PUC

DAC Channel C Power-Up. See PUA description.

R

0

1

DACx_PUB

DAC Channel B Power-Up. See PUA description.

R

0

0

DACx_PUA

DAC Channel A Power-Up

‘0’ when powered down,

‘1’ when powered up.

On detection of an over-current or thermal overtemperature

condition, DAC channel A will power down automatically.

DACx_PUA will be cleared to reflect this.

R

0

Table 3-40: DAC Status Register