TPMC533 User Manual Issue 1.0.1

Page 34 of 107

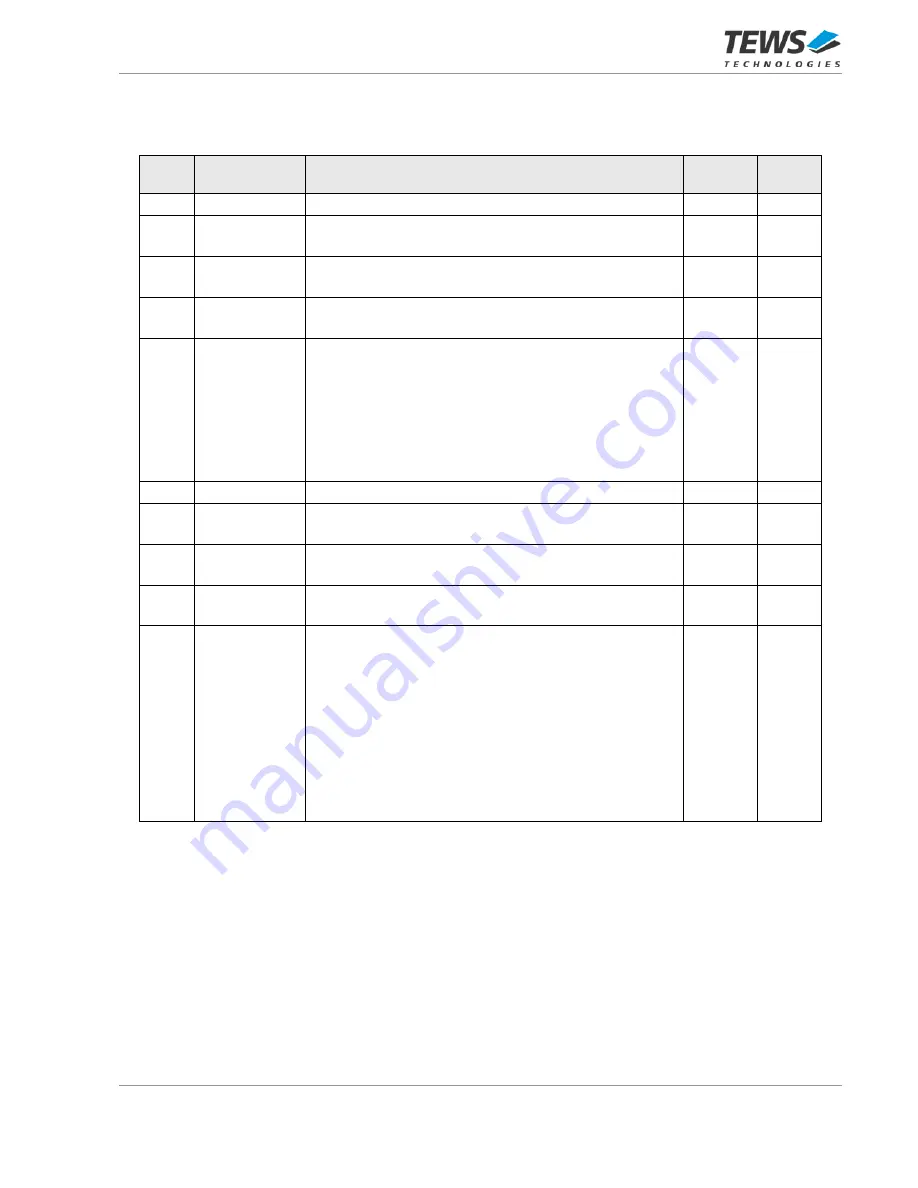

3.2.1.4.2

Global DAC Status Register (0x15C)

For each DAC (for all four DAC Channels of each DAC) on-board the TPMC533, status information can be

read from this read-only register.

Bit

Symbol

Description

Access

Reset

Value

31:12

-

Reserved

-

-

11

DAC4_SETTLE

DAC4 Settle

Refer to the DAC1 Settle bit for description.

R

0

10

DAC3_SETTLE

DAC3 Settle

Refer to the DAC1 Settle bit for description.

R

0

9

DAC2_SETTLE

DAC2 Settle

Refer to the DAC1 Settle bit for description.

R

0

8

DAC1_SETTLE

DAC1 Settle

Indicates the analog output settling time of the four DAC

Channels of DAC1.

Set when DAC1 Channels are settling.

Clear when DAC1 Channels are stable.

This is no physical representation of any kind, just an

internal timer that expires 10µs (typical specified settling

time) after an update of the DAC1 analog outputs.

R

0

7:4

-

Reserved

-

-

3

DAC4_BUSY

DAC4 Busy

Refer to the DAC1 Busy bit for description.

R

0

2

DAC3_BUSY

DAC3 Busy

Refer to the DAC1 Busy bit for description.

R

0

1

DAC2_BUSY

DAC2 Busy

Refer to the DAC1 Busy bit for description.

R

0

0

DAC1_BUSY

DAC1 Busy

Set when

•

Configuration data has been written to DAC1

Configuration Register or is currently transferred to

DAC1

•

Digital values have been written to DAC1 Data

Register or are currently transferred to DAC1

•

Status Read has been requested in DAC1 Status

Register or status data is currently transferred from

DAC1

Clear when DAC1 control logic is in idle state.

R

0

Table 3-32: Global DAC Status Register