TPMC533 User Manual Issue 1.0.1

Page 22 of 107

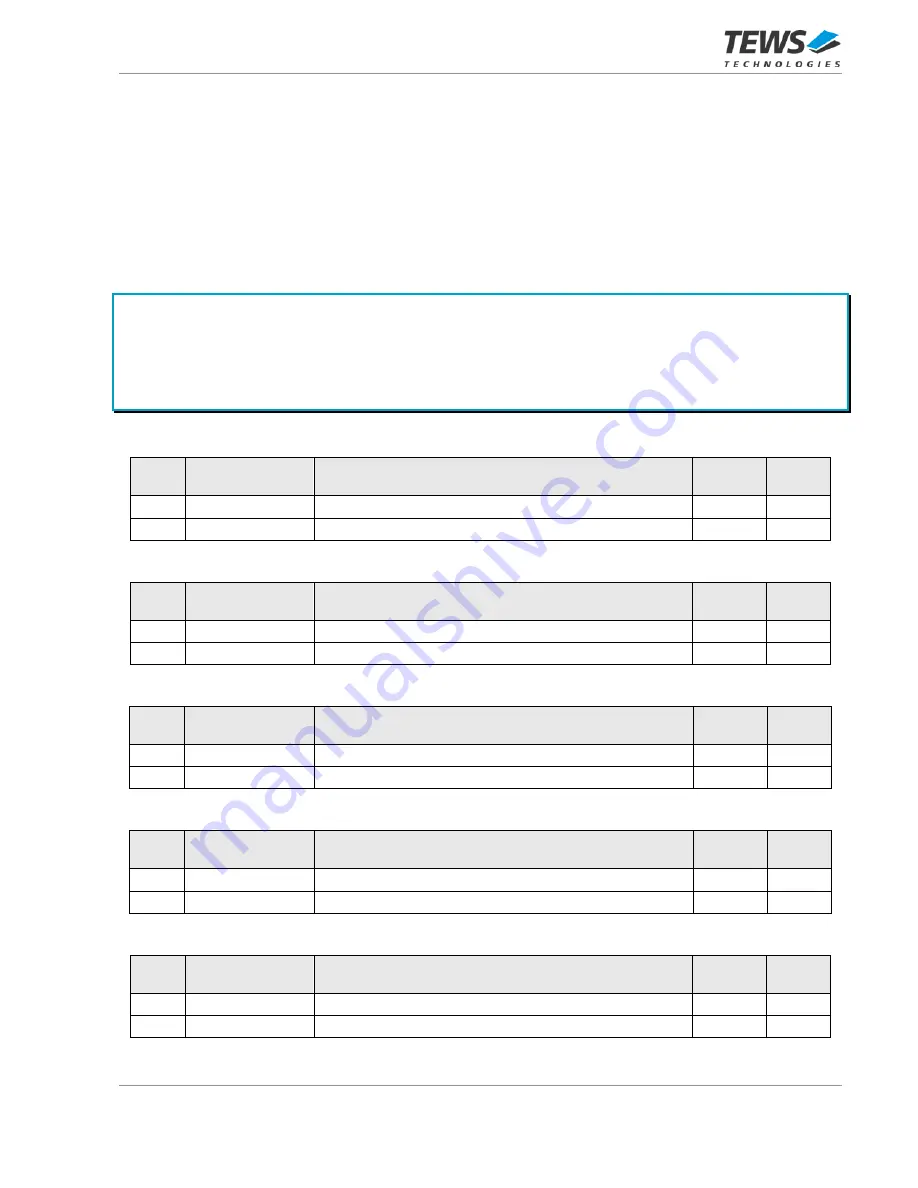

3.2.1.2.2

ADC Correction Registers (0x018, 0x01C, 0x020, 0x024, 0x028, 0x02C, 0x030,

0x034, 0x05C, 0x060, 0x064, 0x068, 0x06C, 0x070, 0x074, 0x078, 0x0A0, 0x0A4,

0x0A8, 0x0AC, 0x0B0, 0x0B4, 0x0B8, 0x0BC, 0x0E4, 0x0E8, 0x0EC, 0x0F0, 0x0F4,

0x0F8, 0x0FC and 0x100)

There are eight dedicated ADC Correction Registers for each ADC (one register for each of the eight ADC

Channels of each ADC).

The correction values for the specific ADC Channels and Voltage Ranges must be read from the Correction

Data ROM at PCI Base Address Register 1 (BAR1).

After power-up and ADC Configuration the ADC Correction Registers should be written with the

values for the desired Voltage Range read from the Correction Data ROM, before switching to

Sequencer Mode or using the ADCs in Manual Mode.

Leaving the ADC Correction Registers unmodified at their Reset Value means that ADC Correction is

disabled.

Bit

Symbol

Description

Access

Reset

Value

31:16

ADCx_GAIN_A

Gain Correction Value ADC Channel A

R/W

0x0000

15:0

ADCx_OFFSET_A

Offset Correction Value ADC Channel A

R/W

0x0000

Table 3-8 : ADC Correction Register A

Bit

Symbol

Description

Access

Reset

Value

31:16

ADCx_GAIN_B

Gain Correction Value ADC Channel B

R/W

0x0000

15:0

ADCx_OFFSET_B

Offset Correction Value ADC Channel B

R/W

0x0000

Table 3-9 : ADC Correction Register B

Bit

Symbol

Description

Access

Reset

Value

31:16

ADCx_GAIN_C

Gain Correction Value ADC Channel C

R/W

0x0000

15:0

ADCx_OFFSET_C

Offset Correction Value ADC Channel C

R/W

0x0000

Table 3-10: ADC Correction Register C

Bit

Symbol

Description

Access

Reset

Value

31:16

ADCx_GAIN_D

Gain Correction Value ADC Channel D

R/W

0x0000

15:0

ADCx_OFFSET_D

Offset Correction Value ADC Channel D

R/W

0x0000

Table 3-11: ADC Correction Register D

Bit

Symbol

Description

Access

Reset

Value

31:16

ADCx_GAIN_E

Gain Correction Value ADC Channel E

R/W

0x0000

15:0

ADCx_OFFSET_E

Offset Correction Value ADC Channel E

R/W

0x0000

Table 3-12: ADC Correction Register E