TPMC533 User Manual Issue 1.0.1

Page 56 of 107

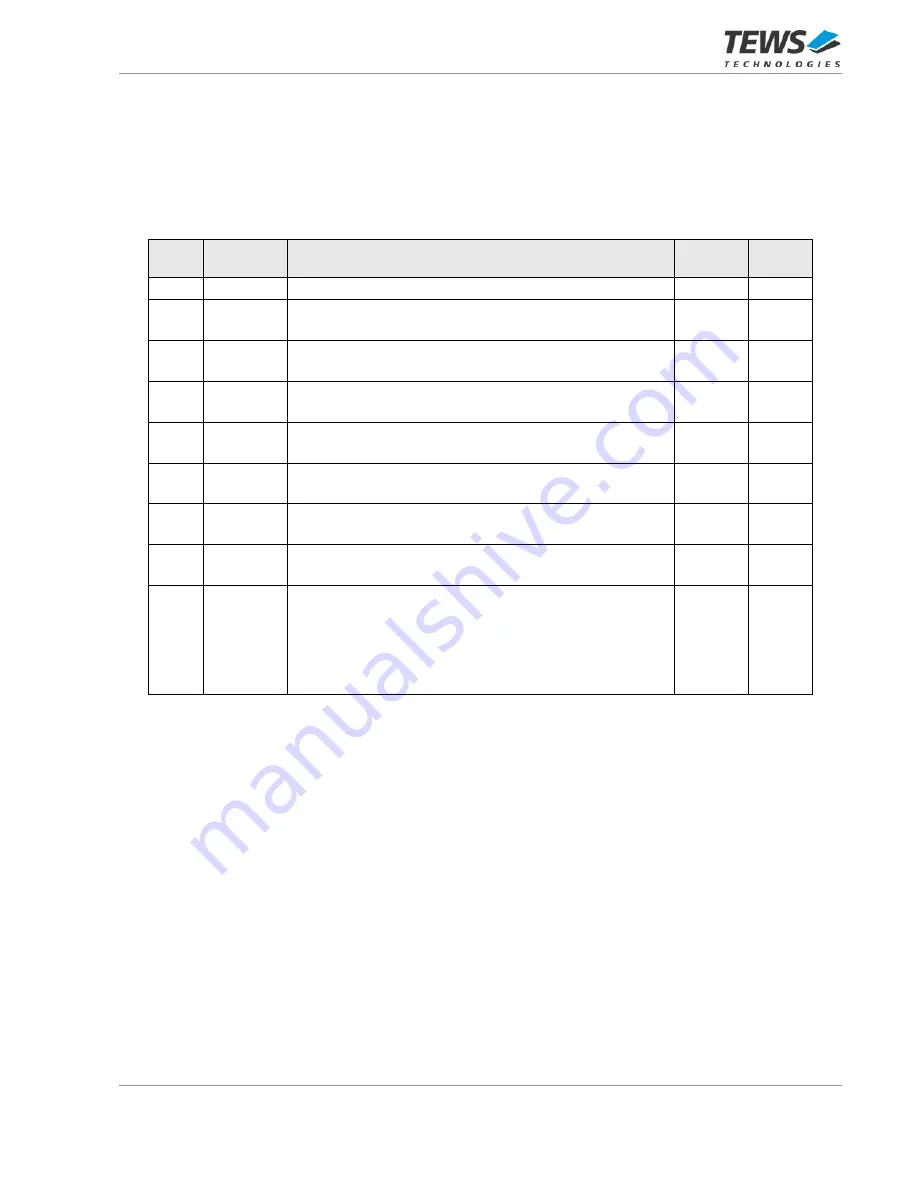

3.2.1.8 DIO Registers

The following registers deal with the Digital I/O interface on the Front I/O connector of the TPMC533.

3.2.1.8.1

DIO Input Register (0x354)

The Digital I/O receivers are always enabled, so each DIO level can always be monitored.

Bit

Symbol

Description

Access

Reset

Value

31:8

-

Reserved

-

-

7

IN8

DIO8 Input

Refer to the DIO1 Input bit for description.

R

0

6

IN7

DIO7 Input

Refer to the DIO1 Input bit for description.

R

0

5

IN6

DIO6 Input

Refer to the DIO1 Input bit for description.

R

0

4

IN5

DIO5 Input

Refer to the DIO1 Input bit for description.

R

0

3

IN4

DIO4 Input

Refer to the DIO1 Input bit for description.

R

0

2

IN3

DIO3 Input

Refer to the DIO1 Input bit for description.

R

0

1

IN2

DIO2 Input

Refer to the DIO1 Input bit for description.

R

0

0

IN1

DIO1 Input

Reflects the actual input state of Digital I/O 1 at all times,

even if DIO1 is configured as output in the DIO Direction

Register

0: Digital I/O 1 is logic low.

1: Digital I/O 1 is logic high.

R

0

Table 3-58: DIO Input Register