Section 19

Controller Area Network (RCAN-TL1)

Rev. 0.50 May 18, 2006 Page 973 of 1588

REJ09B0313-0050

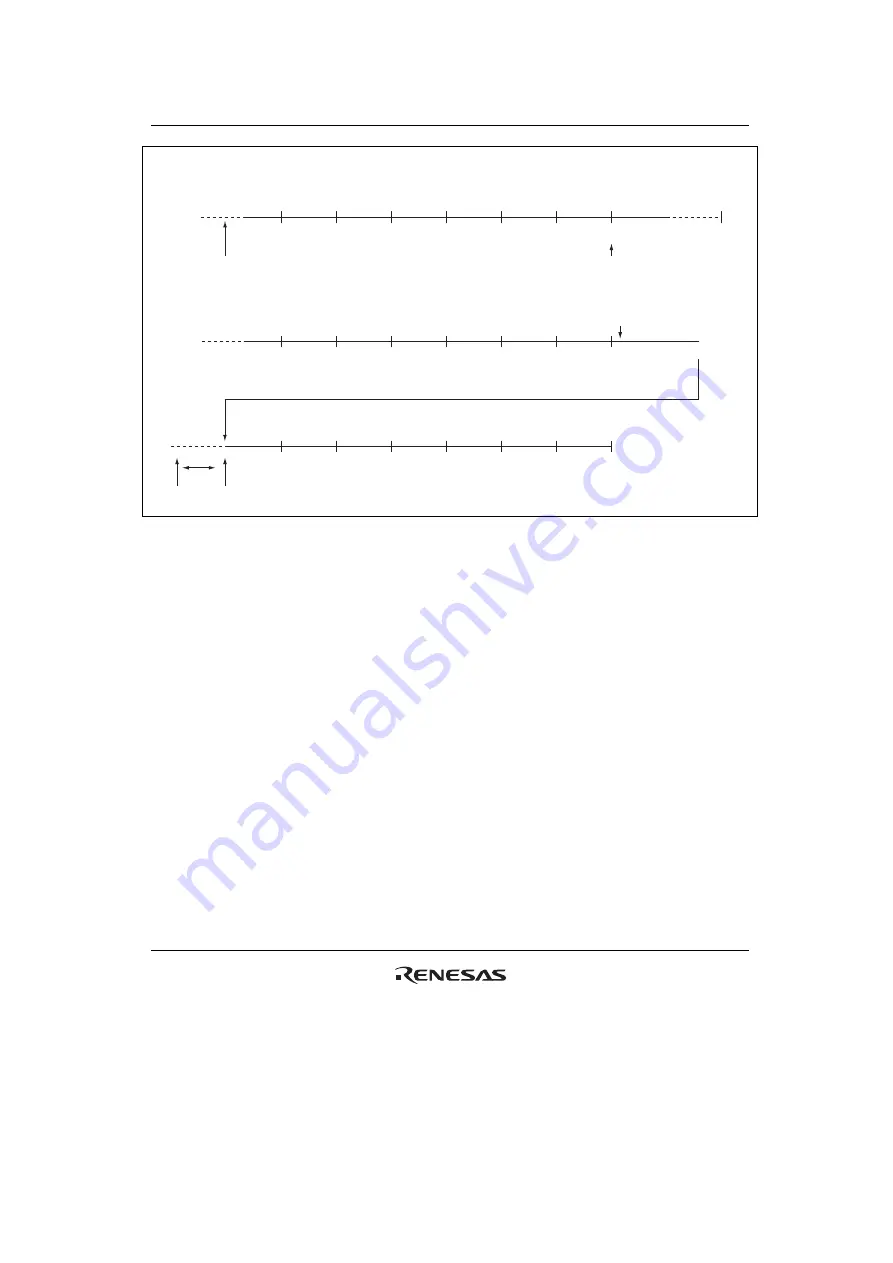

Watch_Trigger

TCMR2

<Configuration> Cycle Time varies between L and Ti L

Slave

Cycle Time = 0 = L

Cycle Time

= Time_Ref

= Ti L

CCR = 1

CCR = 0

CCR = 0

capture timestamp

at SOF of reception

Ref_Mark and CCR are updated

at successful end of time reference reception

= Ti L

= Time_Ref

Time_Mark 1

TTT in MB24

Time_Mark 2

TTT in MB25

Time_Mark 3

TTT in MB26

Time_Mark 4

TTT in MB27

Time_Mark 5

TTT in MB28

Time_Mark 6

TTT in MB29

Time_Ref

TTT in MB30

Time_Mark 1

TTT in MB24

Time_Mark 2

TTT in MB25

Time_Mark 3

TTT in MB26

Time_Mark 4

TTT in MB27

Time_Mark 5

TTT in MB28

Time_Mark 6

TTT in MB29

Time_Ref

TTT in MB30

Time_Mark 1

TTT in MB24

Time_Mark 2

TTT in MB25

Time_Mark 3

TTT in MB26

Time_Mark 4

TTT in MB27

Time_Mark 5

TTT in MB28

Time_Mark 6

TTT in MB29

Time_Ref

TTT in MB30

CCR isn't incremented unlike time master

copy CCR from received time reference

<Normal Operation>

L

Figure 19.20 Time Slave

•

Function to be implemented by software

Some of the TTCAN functions need to be implemented in software. The main details are reported

hereafter. Please refer to ISO-11898-4 for more details.

Change from Init_Watch_Trigger to Watch_Trigger

RCAN-TL1 offers the two registers TCMR0 and TCMR2 as H/W support for

Init_Watch_Trigger and Watch_Trigger respectively. The SW is requested to enable

TCMR0 and disable TCMR2 up to the first reference message is detected on the CAN Bus

and then disable TCMR0 and enable TCMR2.- Schedule Synchronization state machine.

Only reception of Next_is_Gap interrupt is supported. The application needs to take care of

stopping all transmission at the end of the current basic cycle by setting the related TXCR

flags.Master-Slave Mode control.

Only automatic cycle time synchronization and CCR increment is supported.

Message status count

Software has to count scheduling errors for periodic messages in exclusive windows.

Summary of Contents for Single-Chip Microcomputer SH7203

Page 2: ...Rev 0 50 May 18 2006 Page ii of xxx ...

Page 30: ...Rev 0 50 May 18 2006 Page xxx of xxx ...

Page 52: ...Section 1 Overview Rev 0 50 May 18 2006 Page 22 of 1588 REJ09B0313 0050 ...

Page 98: ...Section 2 CPU Rev 0 50 May 18 2006 Page 68 of 1588 REJ09B0313 0050 ...

Page 128: ...Section 4 Clock Pulse Generator CPG Rev 0 50 May 18 2006 Page 98 of 1588 REJ09B0313 0050 ...

Page 200: ...Section 6 Interrupt Controller INTC Rev 0 50 May 18 2006 Page 170 of 1588 REJ09B0313 0050 ...

Page 242: ...Section 8 Cache Rev 0 50 May 18 2006 Page 212 of 1588 REJ09B0313 0050 ...

Page 400: ...Section 9 Bus State Controller BSC Rev 0 50 May 18 2006 Page 370 of 1588 REJ09B0313 0050 ...

Page 696: ...Section 13 Watchdog Timer WDT Rev 0 50 May 18 2006 Page 666 of 1588 REJ09B0313 0050 ...

Page 726: ...Section 14 Realtime Clock RTC Rev 0 50 May 18 2006 Page 696 of 1588 REJ09B0313 0050 ...

Page 876: ...Section 17 I2 C Bus Interface 3 IIC3 Rev 0 50 May 18 2006 Page 846 of 1588 REJ09B0313 0050 ...

Page 1054: ...Section 21 D A Converter DAC Rev 0 50 May 18 2006 Page 1024 of 1588 REJ09B0313 0050 ...

Page 1294: ...Section 24 LCD Controller LCDC Rev 0 50 May 18 2006 Page 1264 of 1588 REJ09B0313 0050 ...

Page 1386: ...Section 26 I O Ports Rev 0 50 May 18 2006 Page 1356 of 1588 REJ09B0313 0050 ...

Page 1512: ...Section 30 List of Registers Rev 0 50 May 18 2006 Page 1482 of 1588 REJ09B0313 0050 ...

Page 1598: ...Section 31 Electrical Characteristics Rev 0 50 May 18 2006 Page 1568 of 1588 REJ09B0313 0050 ...

Page 1606: ...Appendix Rev 0 50 May 18 2006 Page 1576 of 1588 REJ09B0313 0050 ...

Page 1618: ...Rev 0 50 May 18 2006 Page 1588 of 1588 REJ09B0313 0050 ...

Page 1621: ......

Page 1622: ...SH7203 Group Hardware Manual ...