Part II: PCM-959/phyCORE-OMAP44xx Carrier Board

phyCORE-OMAP44xx

150

©

PHYTEC Messtechnik GmbH

2012

L-760e_1

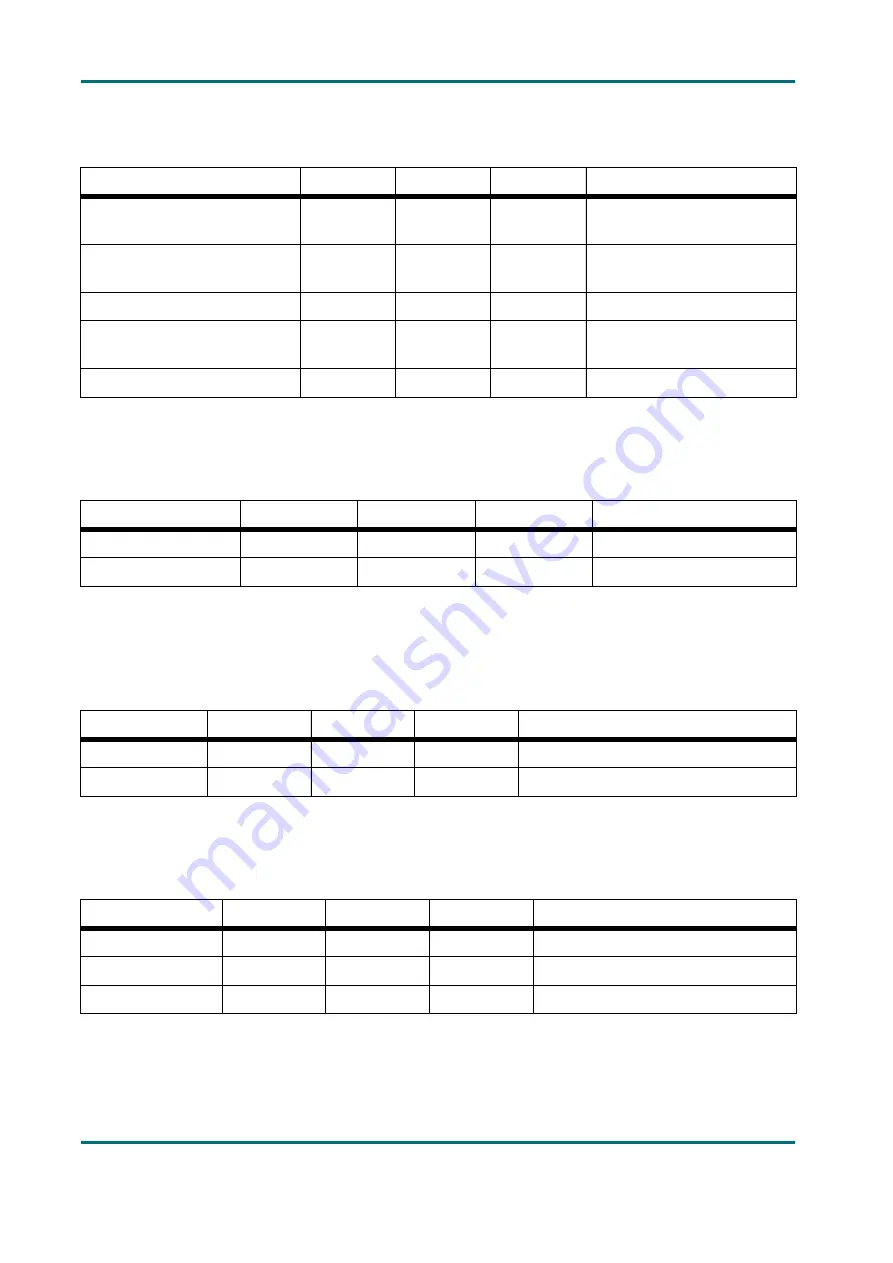

2.1.3.21.8 PMIC Signal Mapping

The expansion connector X5 provides the PMIC control and status signals of the phyCORE-OMAP44xx

2.1.3.21.9 USBC1 Signal Mapping

The expansion connector X5 provides the USBC1 signals of the phyCORE-OMAP44xx.

2.1.3.21.10 Audio Speaker Mapping

The expansion connector X5 provides the Audio Speaker signals of the Audio device driver TLV320AIC3007

(U43). X24 - Speaker Out - maximal 1 Watt into a differential 8 Ohm load

2.1.3.21.11 Control Signal Mapping

The expansion connector X5 provides the control signals of the phyCORE-OMAP44xx.

Signal

Pin #

I/O

SL

Description

X_PMIC_SYSEN

X5C38

O

1.8 V

Sysen output for switching an

extern power source

X_PMIC_EXTCHRG_ENZ

X5C39

O

1.8 V

Control output to extern

Loading-IC

X_PMIC_VAC

X5C40

I

-

extern VAC charger input

X_PMIC_CHRG_EXTCHRG_STATZ X5C41

I

1.8 V

Status input from extern

Loading-IC

X_PMIC_CLK32KAUDIO

X5D37

O

1.8 V

32K Clock

Table 77:

PMIC Signal Mapping

Signal

Pin #

I/O

SL

Description

X_USBC1_ICUSB_DP

X5D12

I/O

USB

USBC1 data plus

X_USBC1_ICUSB_DM

X5D13

I/O

USB

USBC1 data minus

Table 78:

USBC1 Signal Mapping

Signal

Pin #

I/O

SL

Description

SPEAKER_SPOM

X5D22

O

AUDIO

Speaker negative differential output

SPEAKER_SPOP

X5D23

O

AUDIO

Speaker positive differential output

Table 79:

Audio Speaker Mapping

Signal

Pin #

I/O

SL

Description

X_nRESET_WARM

X5D39

I

1.8 V

WARM Reset Signal

X_nRESET_PWRON

X5D40

I/O

1.8 V

Power On Reset Signal

X_nRESET_PER

X5D41

I/O

1.8 V

PER Reset Signal

Table 80:

System Signal Mapping