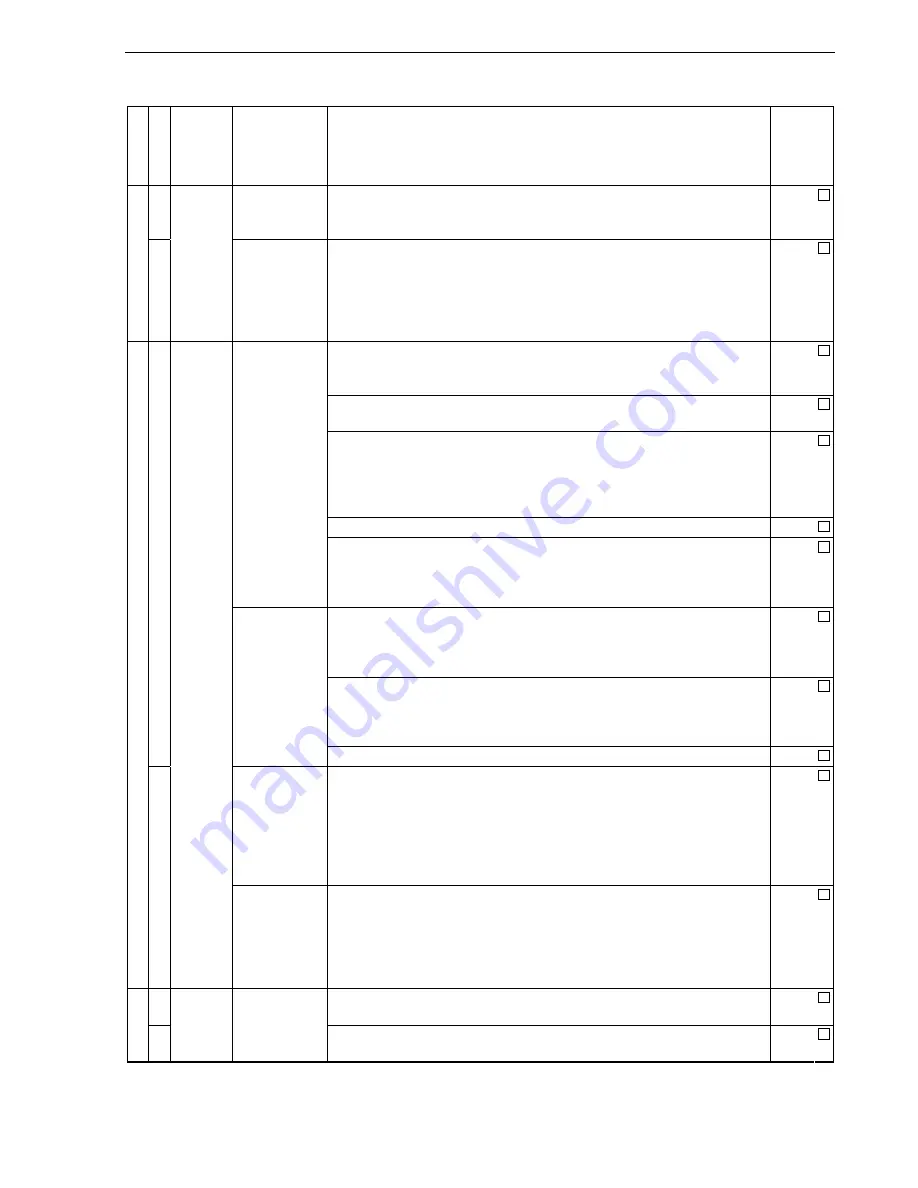

APPENDIX D LIST OF CAUTIONS

User’s Manual U16899EJ2V0UD

525

(11/24)

Chapter

Cl

assi

fi

cati

on

Function Details

of

Function

Cautions Page

Soft

WTM: Watch

timer operation

mode register

Do not change the count clock and interval time (by setting bits 4 to 7 (WTM4 to

WTM7) of WTM) during watch timer operation.

p. 227

Chapter 9

Hard

Watch

timer

Interrupt

request

When operation of the watch timer and 5-bit counter is enabled by the watch timer

mode control register (WTM) (by setting bits 0 (WTM0) and 1 (WTM1) of WTM to

1), the interval until the first interrupt request (INTWT) is generated after the

register is set does not exactly match the specification made with bits 2 and 3

(WTM2 and WTM3) of WTM. Subsequently, however, the INTWT signal is

generated at the specified intervals.

p. 230

If data is written to WDTM, a wait cycle is generated. Do not write data to WDTM

when the CPU is operating on the subsystem clock and the high-speed system

clock is stopped. For details, see CHAPTER 32 CAUTIONS FOR WAIT.

p. 235

Set bits 7, 6, and 5 to 0, 1, and 1, respectively (when “Ring-OSC cannot be

stopped” is selected by the option byte, other values are ignored).

p. 235

After reset is released, WDTM can be written only once by an 8-bit memory

manipulation instruction. If writing attempted a second time, an internal reset

signal is generated. If the source clock to the watchdog timer is stopped,

however, an internal reset signal is generated when the source clock to the

watchdog timer resumes operation.

p. 235

WDTM cannot be set by a 1-bit memory manipulation instruction.

p. 235

WDTM:

Watchdog timer

mode register

If “Ring-OSC can be stopped by software” is selected by the option byte and the

watchdog timer is stopped by setting WDCS4 to 1, the watchdog timer does not

resume operation even if WDCS4 is cleared to 0. In addition, the internal reset

signal is not generated.

p. 235

If a value other than ACH is written to WDTE, an internal reset signal is

generated. If the source clock to the watchdog timer is stopped, however, an

internal reset signal is generated when the source clock to the watchdog timer

resumes operation.

p. 235

If a 1-bit memory manipulation instruction is executed for WDTE, an internal reset

signal is generated. If the source clock to the watchdog timer is stopped,

however, an internal reset signal is generated when the source clock to the

watchdog timer resumes operation.

p. 235

Soft

WDTE:

Watchdog timer

enable register

The value read from WDTE is 9AH (this differs from the written value (ACH)).

p. 235

When “Ring-

OSC cannot be

stopped” is

selected by

option byte

In this mode, operation of the watchdog timer absolutely cannot be stopped even

during STOP instruction execution. For 8-bit timer H1 (TMH1), a division of the

Ring-OSC can be selected as the count source, so clear the watchdog timer using

the interrupt request of TMH1 before the watchdog timer overflows after STOP

instruction execution. If this processing is not performed, an internal reset signal

is generated when the watchdog timer overflows after STOP instruction

execution.

p. 237

Chapter 10

Hard

Watchdog

timer

When “Ring-

OSC can be

stopped by

software” is

selected by

option byte

In this mode, watchdog timer operation is stopped during HALT/STOP instruction

execution. After HALT/STOP mode is released, counting is started again using

the operation clock of the watchdog timer set before HALT/STOP instruction

execution by WDTM. At this time, the counter is not cleared to 0 but holds its

value.

p. 238

Soft

A/D conversion must be stopped before rewriting bits FR0 to FR2 to values other

than the identical data.

p. 250

Chapter 12

Hard

A/D

converter

ADM: A/D

converter mode

register

For the sampling time of the A/D converter and the A/D conversion start delay

time, see (11) in 12.6 Cautions for A/D Converter.

p. 250