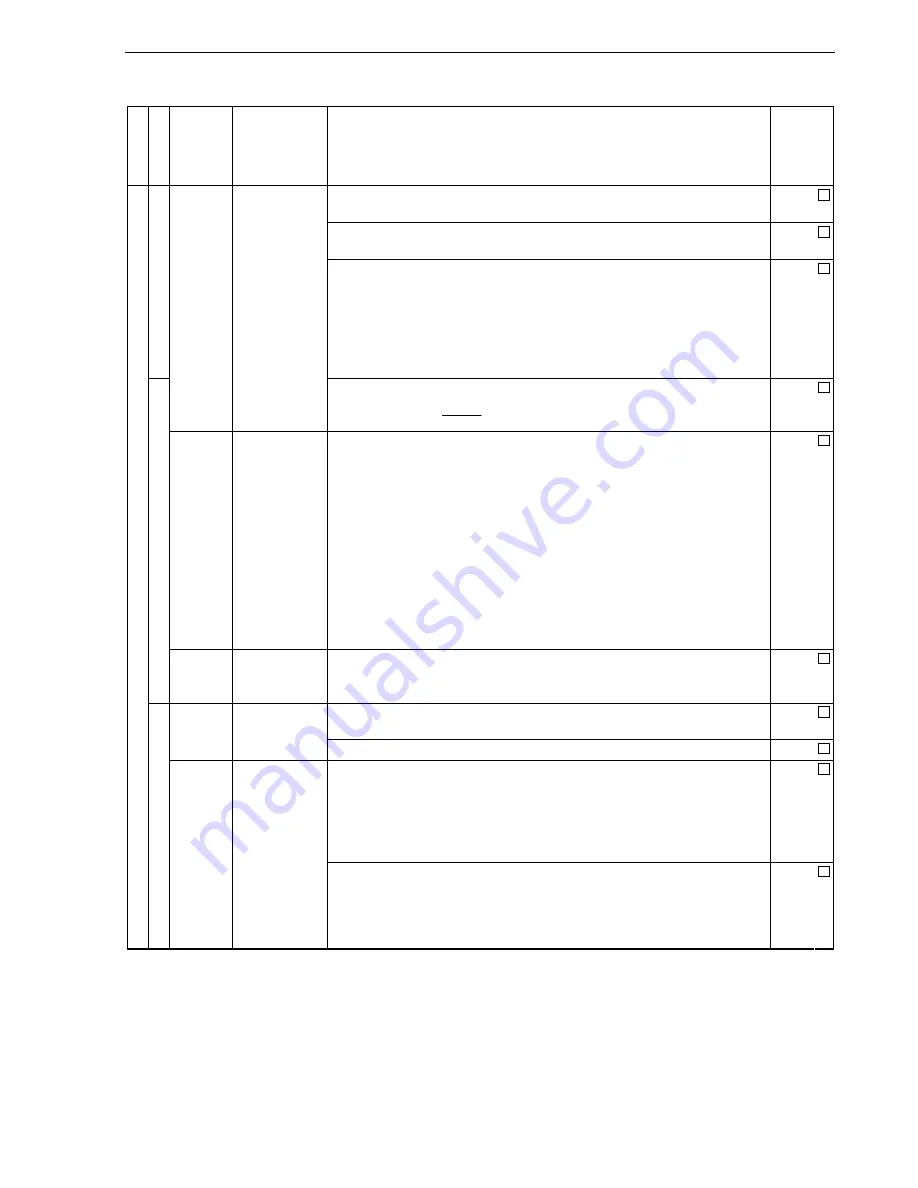

APPENDIX D LIST OF CAUTIONS

User’s Manual U16899EJ2V0UD

517

(3/24)

Chapter

Cl

assi

fi

cati

on

Function Details

of

Function

Cautions Page

To set the STOP mode when the high-speed system clock is used as the CPU

clock, set OSTS before executing a STOP instruction.

p. 117

Before setting OSTS, confirm with OSTC that the desired oscillation stabilization

time has elapsed.

p. 117

Soft

If the STOP mode is entered and then released while the Ring-OSC clock is being

used as the CPU clock, set the oscillation stabilization time as follows.

•

Desired OSTC oscillation stabilization time

≤

Oscillation stabilization time set by

OSTS

The oscillation stabilization time counter counts up to the oscillation stabilization

time set by OSTS. Note, therefore, that only the status up to the oscillation

stabilization time set by OSTS is set to OSTC after STOP mode is released.

p. 117

Main

clock

OSTS:

Oscillation

stabilization

time select

register

The wait time when STOP mode is released does not include the time after STOP

mode release until clock oscillation starts (“a” below) regardless of whether STOP

mode is released by RESET input or interrupt generation.

p. 117

High-

speed

system

clock

oscillator,

subsystem

clock

oscillator

−

When using the high-speed system clock oscillator and subsystem clock

oscillator, wire as follows in the area enclosed by the broken lines in the Figures

5-8 and 5-9 to avoid an adverse effect from wiring capacitance.

•

Keep the wiring length as short as possible.

•

Do not cross the wiring with the other signal lines.

•

Do not route the wiring near a signal line through which a high fluctuating

current

flows.

•

Always make the ground point of the oscillator capacitor the same potential as

V

SS

. Do not ground the capacitor to a ground pattern through which a high

current

flows.

•

Do not fetch signals from the oscillator.

Note that the subsystem clock oscillator is designed as a low-amplitude circuit for

reducing power consumption.

p. 119

Hard

Prescaler

−

When the Ring-OSC clock is selected as the clock supplied to the CPU, the

prescaler generates various clocks by dividing the Ring-OSC oscillator output (f

X

=

240 kHz (TYP.)).

p. 121

The RSTOP setting is valid only when “Can be stopped by software” is set for

Ring-OSC by the option byte.

p. 128

Ring-OSC

−

To calculate the maximum time, set f

R

= 120 kHz.

p. 129

Selection of the CPU clock cycle division factor (PCC0 to PCC2) and switchover

from the high-speed system clock to the subsystem clock (changing CSS from 0

to 1) should not beset simultaneously.

Simultaneous setting is possible, however, for selection of the CPU clock cycle

division factor (PCC0 to PCC2) and switchover from the subsystem clock to the

high-speed system clock (changing CSS from 1 to 0).

p. 130

Chapter 5

Soft

CPU

clock

−

While the CPU is operating on Ring-OSC, setting the following values is

prohibited.

•

CSS, PCC2, PCC1, PCC0 = 0, 0, 1, 0

•

CSS, PCC2, PCC1, PCC0 = 0, 0, 1, 1

•

CSS, PCC2, PCC1, PCC0 = 0, 1, 0, 0

p. 130