CHAPTER 5 CLOCK GENERATOR

Preliminary User’s Manual U16315EJ1V0UD

106

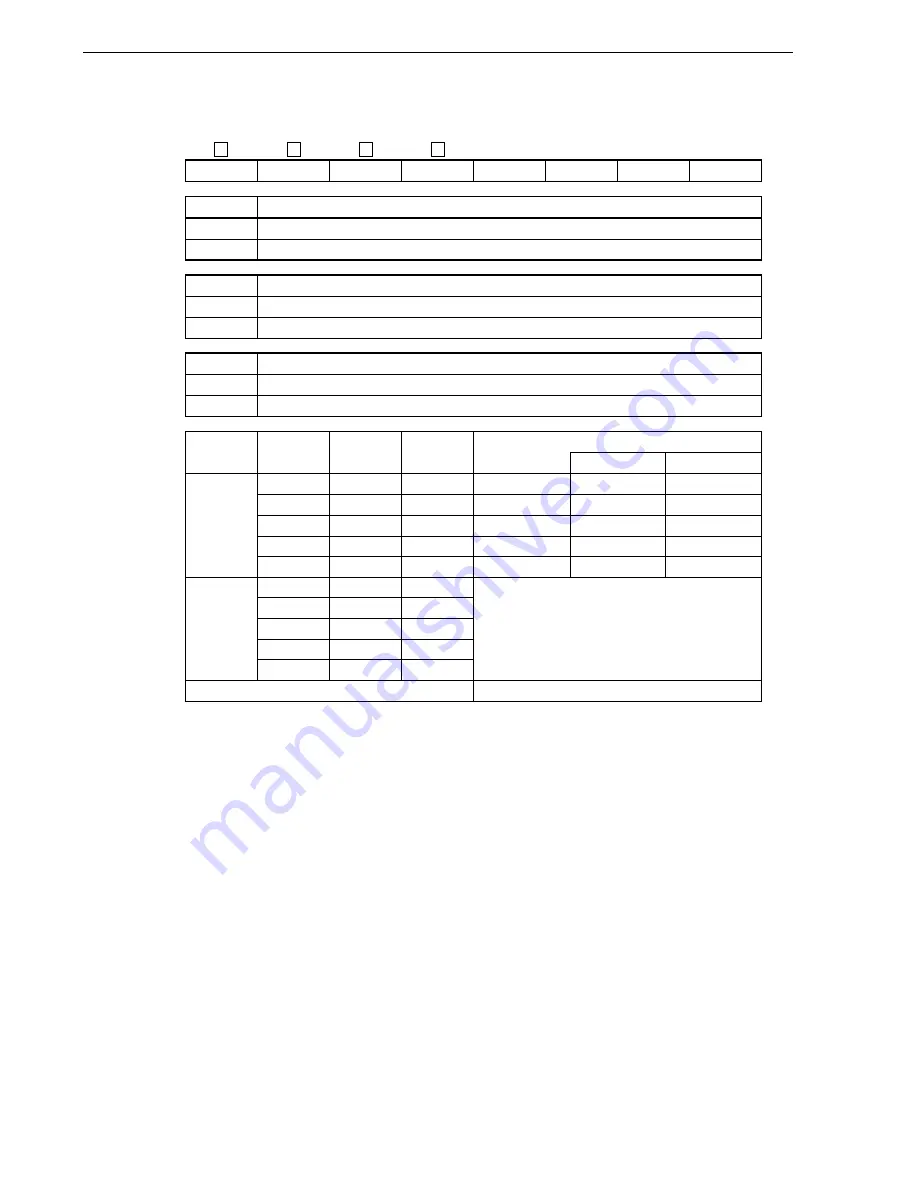

Figure 5-3. Format of Processor Clock Control Register (PCC)

Address: FFFBH After reset: 00H R/W

Note 1

Symbol

7

6

5

4

3

2

1

0

PCC

MCC

FRC

CLS

CSS

0

PCC2

PCC1

PCC0

MCC

Control of X1 oscillator operation

Note 2

0

Oscillation possible

1

Oscillation stopped

FRC

Subsystem clock feedback resistor selection

Note 3

0

On-chip feedback resistor used

1

On-chip feedback resistor not used

CLS

CPU clock status

0

X1 input clock or Ring-OSC clock

1

Subsystem clock

CPU Clock (f

CPU

) Selection

CSS

Note 4

PCC2

PCC1

PCC0

MCM0 = 0

MCM0 = 1

0

0

0

f

X

f

R

f

XP

0

0

1

f

X

/2

f

R

/2

f

XP

/2

0

1

0

f

X

/2

2

f

R

/2

2

f

XP

/2

2

0

1

1

f

X

/2

3

f

R

/2

3

f

XP

/2

3

0

1

0

0

f

X

/2

4

f

R

/2

4

f

XP

/2

4

0

0

0

0

0

1

0

1

0

0

1

1

1

1

0

0

f

XT

/2

Other than above

Setting prohibited

Notes 1.

Bit 5 is read-only.

2.

When the CPU is operating on the subsystem clock, MCC should be used to stop the X1 oscillator

operation. When the CPU is operating on the Ring-OSC clock, use bit 7 (MSTOP) of the main OSC

control register (MOC) to stop the X1 oscillator operation (this cannot be set by MCC). A STOP

instruction should not be used.

3.

The feedback resistor is required to adjust the bias point of the oscillation waveform to close to the

middle of the power supply voltage. Setting FRC to 1 can further reduce the current consumption in

the STOP mode, but only when the subsystem clock is not used.

4.

Be sure to switch CSS from 1 to 0 when bits 1 (MCS) and 0 (MCM0) of the main clock mode register

(MCM) are 1.

Caution

Be sure to set bit 3 to 0.

Remarks 1.

MCM0: Bit 0 of the main clock mode register (MCM)

2.

f

X

:

Main system clock oscillation frequency (X1 input clock oscillation frequency or Ring-OSC clock

oscillation frequency)

3.

f

R

:

Ring-OSC clock oscillation frequency

4.

f

XP

: X1 input clock oscillation frequency

5.

f

XT

: Subsystem clock oscillation frequency