CHAPTER 5 CLOCK GENERATOR

Preliminary User’s Manual U16315EJ1V0UD

121

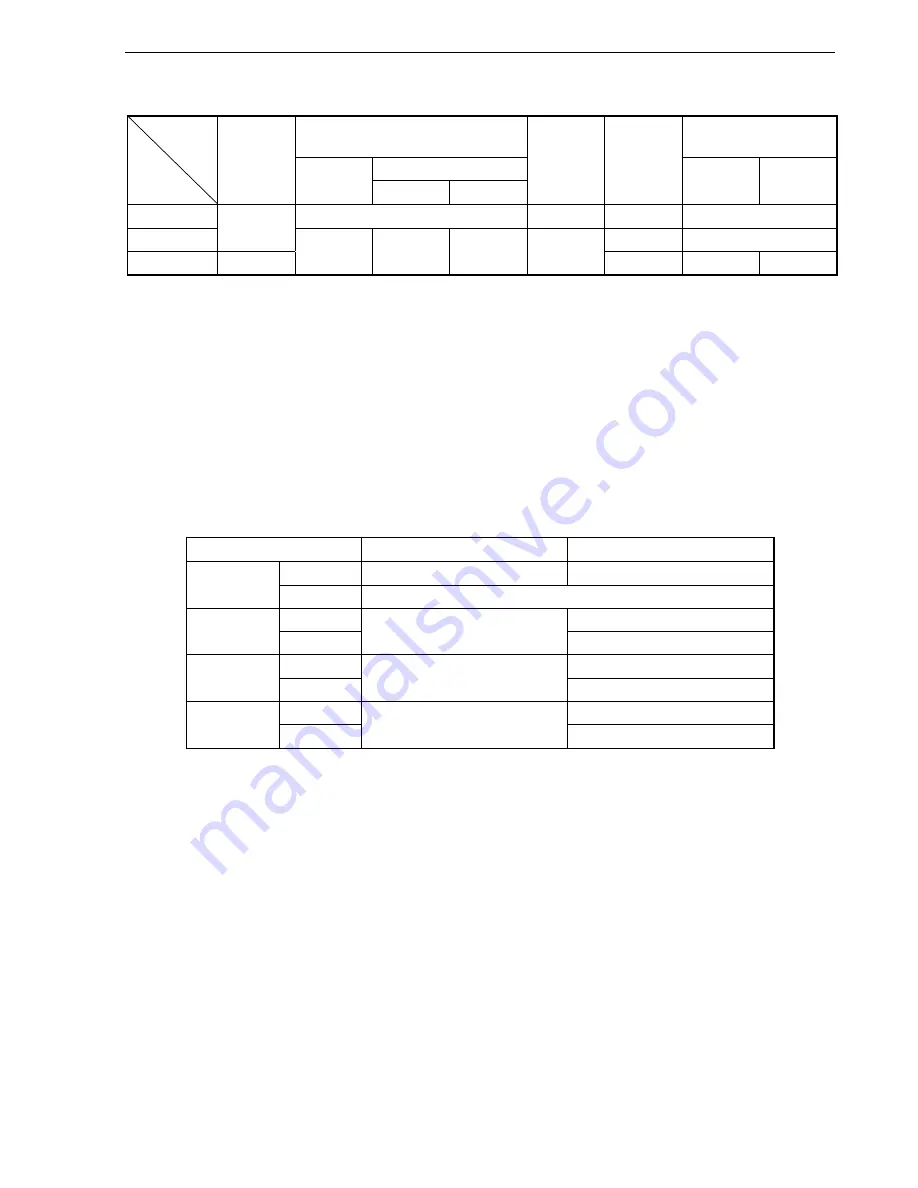

Table 5-3. Relationship Between Operation Clocks in Each Operation Status

Ring-OSC Oscillator

Prescaler Clock Supplied

to Peripherals

Note 2

Status

Operation

Mode

X1

Oscillator

Note 1

RSTOP = 0

RSTOP = 1

Subsystem

Clock

Oscillator

CPU Clock

After

Release

MCM0 = 0

MCM0 = 1

Reset

Stopped

Stopped

Ring-OSC

Stopped

STOP

Stopped

Note 3

Stopped

HALT

Oscillating

Oscillating

Oscillating

Stopped

Oscillating

Note 4

Ring-OSC

X1

Caution

The RSTOP setting is valid only when “Can be stopped by software” is set for Ring-OSC by a mask

option.

Notes 1.

When “Cannot be stopped” is selected for Ring-OSC by a mask option.

2.

When “Can be stopped by software” is selected for Ring-OSC by a mask option.

3.

Operates using the CPU clock at STOP instruction execution.

4.

Operates using the CPU clock at HALT instruction execution.

Remark

RSTOP: Bit 0 of the Ring-OSC mode register (RCM)

MCM0:

Bit 0 of the main clock mode register (MCM)

Table 5-4. Oscillation Control Flags and Clock Oscillation Status

X1 Oscillator

Ring-OSC Oscillator

RSTOP = 0

Stopped

Oscillating

MSTOP = 1

Note

RSTOP = 1

Setting prohibited

RSTOP = 0

Oscillating

MSTOP = 0

Note

RSTOP = 1

Oscillating

Stopped

RSTOP = 0

Oscillating

MCC = 1

Note

RSTOP = 1

Stopped

Stopped

RSTOP = 0

Oscillating

MCC = 0

Note

RSTOP = 1

Oscillating

Stopped

Note

Setting X1 oscillator oscillating/stopped differs depending on the CPU clock used.

•

When the Ring-OSC clock is used as the CPU clock: Set using the MSTOP bit

•

When the subsystem clock is used as the CPU clock: Set using the MCC bit

Caution

The RSTOP setting is valid only when “Can be stopped by software” is set for Ring-OSC

by a mask option.

Remark

MSTOP: Bit 7 of the main OSC control register (MOC)

MCC:

Bit 7 of the processor clock control register (PCC)

RSTOP: Bit 0 of the Ring-OSC mode register (RCM)