MAX32660 User Guide

Maxim Integrated

Page 155 of 195

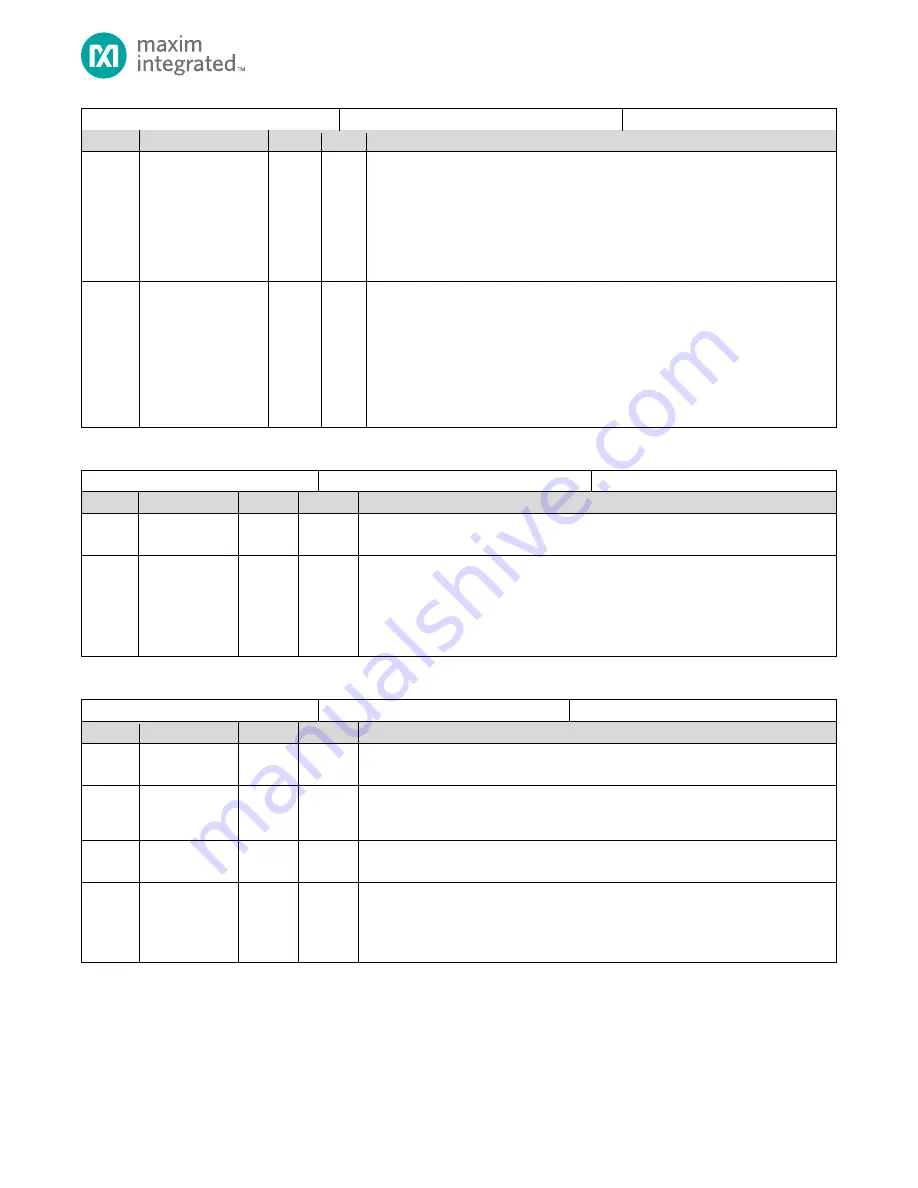

I

2

C Transmit Control Register 1

I2Cn_TXCTRL1

[0x0028]

Bits

Name

Access Reset Description

1

txlast

R/W1O

0

Slave Mode Transmit Last

This bit decides what to do if the I

2

C is in Slave Mode, is transmitting data to a

Master, and the TX FIFO is empty.

0: Hold SCL low. This pauses transmission until data is written to the TX FIFO.

1: End transaction by releasing SCL.

Cleared on a STOP/RESTART condition, or if

txloi

=1 (transmit FIFO

locked for writing).

0

txrdy

R/W1O

1

Transmit FIFO Preload Ready Status

When TX FIFO Preload Mode is enabled,

txpreld

= 1, this bit is

automatically cleared to 0. While this bit is 0, if the I

2

C hardware receives a slave

address match a NACK is sent. Once the I

2

C hardware is ready (firmware has

preloaded the TX FIFO, configured the DMA, etc.) application firmware must set this

bit to 1 so the I

2

C hardware will send an ACK on a slave address match.

When TX FIFO Preload Mode is disabled,

txpreld

= 1, this bit is forced

to 1 and the I

2

C hardware behaves normally.

Table 12-15: I

2

C Data Registers

I

2

C Data Register

I2Cn_FIFO

[0x002C]

Bits

Name

Access

Reset

Description

31:8

-

R/W

0

Reserved for Future Use

Do not modify this field.

7:0

data

R/W

0xFF

I

2

C FIFO Data Register

Reading from this register pops data from the RX FIFO and writes to this register

pushes data onto the TX FIFO. If the RX FIFO is empty, reading this field returns 0xFF.

Note: If the RX FIFO is empty, reads from this field return 0xFF.

Note: If the TX FIFO is full, writes to this field are ignored.

Table 12-16: I

2

C Master Mode Control Registers

I

2

C Master Mode Control Register

I2Cn_MSTR_MODE

[0x0030]

Bits

Name

Access

Reset

Description

31:8

-

R/W

0

Reserved for Future Use

Do not modify this field.

7

sea

R/W

0

Slave Extended Addressing

0: Send a 7-bit address to the slave

1: Send a 10-bit address to the slave

6:3

-

R/W

0

Reserved for Future Use

Do not modify this field.

2

stop

R/W1O

0

Send STOP Condition

0: Stop condition completed or inactive.

1: Send a STOP Condition

Note: This bit is automatically cleared by hardware when the STOP condition begins.