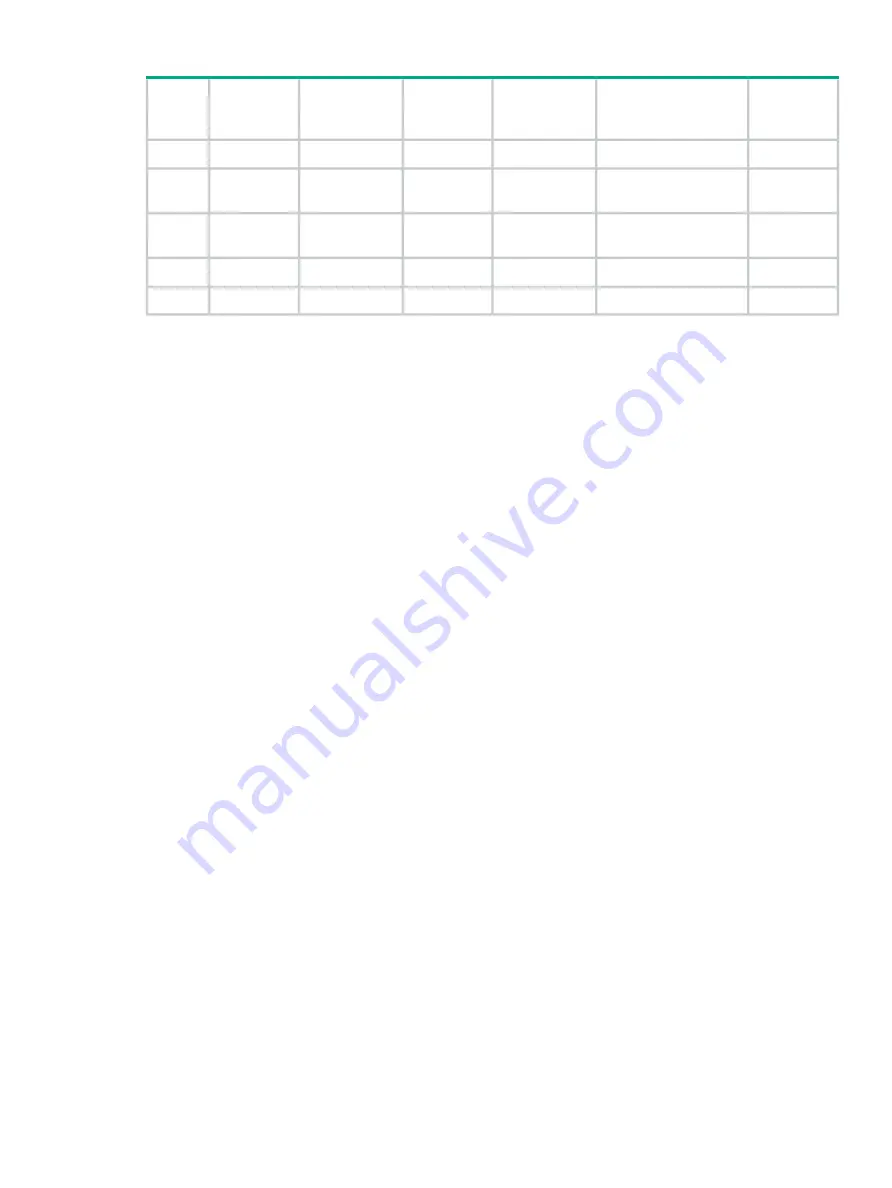

Table 3 PCI/PCI-X/PCIe I/O Rope Groups (continued)

Hot

Swap/OLR

Function

Speed

Bits

Logical Rope

Numbers

Physical

Rope

Numbers

Slot #

Y

PCIe x8 (Public)

2.5 Gbps

x8

3

4, 5, 6, 7

6

Y

High-Speed PCI-X

(Public)

133 MHz

64

2

2, 3

7

Y

High-Speed PCI-X

(Public)

133 MHz

64

5

9

8

Y

General PCI-X (Public)

66 MHz

64

1

1

9, 10

N

UCIO (Private)

33 MHz

32

0

0

-

PCIe MPS Optimization

For PCIe-based systems, each PCIe device has a configurable MPS (maximum payload size)

parameter. Larger MPS values can enable the optimization to gain higher performance. MPS

Optimization is supported on PCIe systems running HP-UX, OpenVMS, and Linux. System

firmware level greater than 02.03 performs an optimization during boot time to set the MPS value

to the largest size supported by both a PCIe root port and the devices below it.

The default server state is optimization disabled. When disabled system firmware sets MPS to

the minimum value on each PCIe device.

The

info io

command will display the current PCIe MPS optimization setting. See

To enable PCIe MPS optimization, use the

ioconfig mps_optimize

command. See

For non-PCIe systems,

ioconfig

and

info io

will not display the MPS optimization policy

setting. The Set PCIe MPS Optimization boot manager menu also will not be displayed. Running

the

ioconfig mps_optimize [on|off]

command from a non-PCIe system, the following

output will be displayed:

-------------

Shell> ioconfig mps_optimize

ioconfig: PCIe MPS optimization is not supported.

Shell> ioconfig mps_optimize on

ioconfig: PCIe MPS optimization is not supported.

Exit status code: Unsupported

Shell>

-----------------

To restore MPS to the default values, use the

default clear

command. See

Processor

The server processor subsystem accommodates one, two, three, or four dual-core Itanium

processor modules. The processor subsystem consists of the following components:

•

zx2 CEC front side bus, memory, and I/O controller

•

System clock generation and distribution

•

Circuitry for manageability and fault detection

The zx2 CEC and the processor modules are located on the processor board assembly. Each

processor connects to the processor board through a zero insertion force (ZIF) socket. The

Server Subsystems

19