301

0

7

15 0

7

15 0

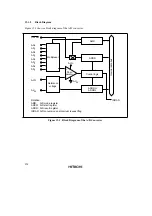

Internal

basic clock

Receive data

(RXD3x)

Start bit

D0

16 clock pulses

8 clock pulses

D1

Synchronization

sampling timing

Data sampling

timing

Figure 10.21 Receive Data Sampling Timing in Asynchronous Mode

Consequently, the receive margin in asynchronous mode can be expressed as shown in equation

(1).

M ={(0.5 –

1

) –

D – 0.5

– (L – 0.5) F}

×

100 [%]

2N

N

..... Equation (1)

where

M: Receive margin (%)

N: Ratio of bit rate to clock (N = 16)

D: Clock duty (D = 0.5 to 1.0)

L: Frame length (L = 9 to 12)

F: Absolute value of clock frequency deviation

Substituting 0 for F (absolute value of clock frequency deviation) and 0.5 for D (clock duty) in

equation (1), a receive margin of 46.875% is given by equation (2).

When D = 0.5 and F = 0,

M = {0.5 — 1/(2

×

16)}

×

100 [%]

= 46.875%

..... Equation (2)

However, this is only a computed value, and a margin of 20% to 30% should be allowed when

carrying out system design.