290

• Simultaneous transmit/receive

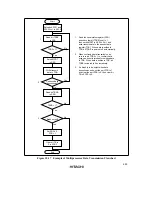

Figure 10.15 shows an example of a flowchart for a simultaneous transmit/receive operation. This

procedure should be followed for simultaneous transmission/reception after initializing SCI3.

Start

End

Read bit TDRE

in SSR

Sets bits SPC31 and

SPC32 to 1 in SPCR

1

2

3

4

Write transmit

data to TDR

Read bit OER

in SSR

Read bit RDRF

in SSR

Clear bits TE and

RE to 0 in SCR3

Yes

TDRE = 1?

No

OER = 1?

No

RDRF = 1?

Yes

Continue data

transmission/reception?

No

Yes

No

Read receive data

in RDR

Yes

Overrun error

processing

Read the serial status register (SSR) and

check that bit TDRE is set to 1, then write

transmit data to the transmit data register

(TDR). When data is written to TDR, bit

TDRE is cleared to 0 automatically.

Read SSR and check that bit RDRF is set

to 1. If it is, read the receive data in RDR.

When the RDR data is read, bit RDRF is

cleared to 0 automatically.

When continuing data transmission/reception,

finish reading of bit RDRF and RDR before

receiving the MSB (bit 7) of the current frame.

Before receiving the MSB (bit 7) of the current

frame, also read TDRE = 1 to confirm that a

write can be performed, then write data to TDR.

When data is written to TDR, bit TDRE is cleared

to 0 automatically, and when the data in RDR is

read, bit RDRF is cleared to 0 automatically.

If an overrun error has occurred, read bit OER

in SSR, and after carrying out the necessary

error processing, clear bit OER to 0. Transmis-

sion and reception cannot be resumed if bit

OER is set to 1.

See figure 10-13 for details on overrun error

processing.

1.

2.

3.

4.

Figure 10.15 Example of Simultaneous Data Transmission/Reception Flowchart

(Synchronous Mode)