378

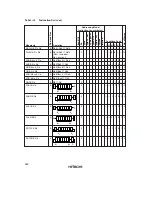

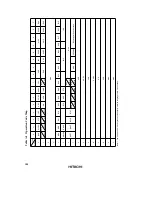

Table A.1 lists the H8/300L CPU instruction set.

Table A.1

Instruction Set

Mnemonic

Operation

I

H N Z V C

MOV.B #xx:8, Rd

B #xx:8

→

Rd8

2

— —

↕

↕

0 — 2

MOV.B Rs, Rd

B Rs8

→

Rd8

2

— —

↕

↕

0 — 2

MOV.B @Rs, Rd

B @Rs16

→

Rd8

2

— —

↕

↕

0 — 4

MOV.B @(d:16, Rs), Rd

B @(d:16, Rs16)

→

Rd8

4

— —

↕

↕

0 — 6

MOV.B @Rs+, Rd

B @Rs16

→

Rd8

2

— —

↕

↕

0 — 6

Rs16+1

→

Rs16

MOV.B @aa:8, Rd

B @aa:8

→

Rd8

2

— —

↕

↕

0 — 4

MOV.B @aa:16, Rd

B @aa:16

→

Rd8

4

— —

↕

↕

0 — 6

MOV.B Rs, @Rd

B Rs8

→

@Rd16

2

— —

↕

↕

0 — 4

MOV.B Rs, @(d:16, Rd)

B Rs8

→

@(d:16, Rd16)

4

— —

↕

↕

0 — 6

MOV.B Rs, @–Rd

B Rd16–1

→

Rd16

2

— —

↕

↕

0 — 6

Rs8

→

@Rd16

MOV.B Rs, @aa:8

B Rs8

→

@aa:8

2

— —

↕

↕

0 — 4

MOV.B Rs, @aa:16

B Rs8

→

@aa:16

4

— —

↕

↕

0 — 6

MOV.W #xx:16, Rd

W #xx:16

→

Rd

4

— —

↕

↕

0 — 4

MOV.W Rs, Rd

W Rs16

→

Rd16

2

— —

↕

↕

0 — 2

MOV.W @Rs, Rd

W @Rs16

→

Rd16

2

— —

↕

↕

0 — 4

MOV.W @(d:16, Rs), Rd W @(d:16, Rs16)

→

Rd16

4

— —

↕

↕

0 — 6

MOV.W @Rs+, Rd

W @Rs16

→

Rd16

2

— —

↕

↕

0 — 6

Rs16+2

→

Rs16

MOV.W @aa:16, Rd

W @aa:16

→

Rd16

4

— —

↕

↕

0 — 6

MOV.W Rs, @Rd

W Rs16

→

@Rd16

2

— —

↕

↕

0 — 4

MOV.W Rs, @(d:16, Rd) W Rs16

→

@(d:16, Rd16)

4

— —

↕

↕

0 — 6

MOV.W Rs, @–Rd

W Rd16–2

→

Rd16

2

— —

↕

↕

0 — 6

Rs16

→

@Rd16

MOV.W Rs, @aa:16

W Rs16

→

@aa:16

4

— —

↕

↕

0 — 6

POP Rd

W @SP

→

Rd16

2

— —

↕

↕

0 — 6

SP+2

→

SP

PUSH Rs

W SP–2

→

SP

2

— —

↕

↕

0 — 6

Rs16

→

@SP

#xx: 8/16

Rn

@Rn

@(d:16, Rn)

@–Rn/@Rn+

@aa: 8/16

@(d:8, PC)

@@aa

Implied

No. of States

Addressing Mode/

Instruction Length (bytes)

Condition Code

O

perand

S

ize