67

3.3.2

Interrupt Control Registers

Table 3.3 lists the registers that control interrupts.

Table 3.3

Interrupt Control Registers

Name

Abbreviation

R/W

Initial Value

Address

IRQ edge select register

IEGR

R/W

H'E0

H'FFF2

Interrupt enable register 1

IENR1

R/W

H'00

H'FFF3

Interrupt enable register 2

IENR2

R/W

H'00

H'FFF4

Interrupt request register 1

IRR1

R/W

*

H'20

H'FFF6

Interrupt request register 2

IRR2

R/W

*

H'00

H'FFF7

Wakeup interrupt request register

IWPR

R/W

*

H'00

H'FFF9

Wakeup edge select register

WEGR

R/W

H'00

H'FF90

Note:

*

Write is enabled only for writing of 0 to clear a flag.

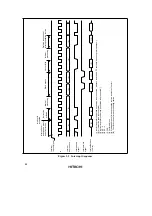

1. IRQ edge select register (IEGR)

Bit

Initial value

Read/Write

7

—

1

—

6

—

1

—

5

—

1

—

4

IEG4

0

R/W

3

IEG3

0

R/W

0

IEG0

0

R/W

2

IEG2

0

R/W

1

IEG1

0

R/W

IEGR is an 8-bit read/write register used to designate whether pins

IRQ

4

to

IRQ

0

are set to rising

edge sensing or falling edge sensing.

Bits 7 to 5: Reserved bits

Bits 7 to 5 are reserved: they are always read as 1 and cannot be modified.

Bit 4: IRQ

4

edge select (IEG4)

Bit 4 selects the input sensing of the

IRQ

4

pin and

ADTRG

pin.

Bit 4

IEG4

Description

0

Falling edge of

IRQ

4

and

ADTRG

pin input is detected

(initial value)

1

Rising edge of

IRQ

4

and

ADTRG

pin input is detected