372

15.3

Operation Timing

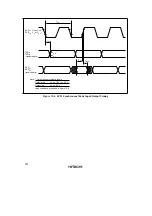

Figures 15.1 to 15.6 show timing diagrams.

t

, tw

OSC

V

IH

V

IL

t

CPH

t

CPL

t

CPr

OSC1

x

1

t

CPf

Figure 15.1 Clock Input Timing

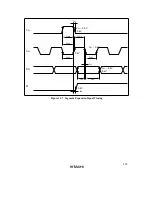

RES

V

IL

t

REL

Figure 15.2 RES Low Width

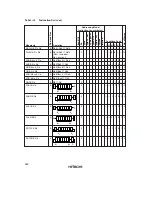

V

IH

V

IL

t

IL

IRQ

0

to IRQ

4

,

WKP

0

to WKP

7

,

ADTRG

,

TMIC, TMIF,

TMIG,

AEVL, AEVH

t

IH

Figure 15.3 Input Timing