6

1.2

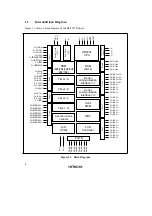

Internal Block Diagram

Figure 1.1 shows a block diagram of the H8/3827R Series.

P1

0

/TMOW

P1

1

/TMOFL

P1

2

/TMOFH

P1

3

/TMIG

P1

4

/

IRQ

4

/

ADTRG

P1

5

/

IRQ

1

/TMIC

P1

6

/

IRQ

2

P1

7

/

IRQ

3

/TMIF

P3

0

/PWM

P3

1

/UD

P3

2

/

RESO

P3

3

/SCK

31

P3

4

/RXD

31

P3

5

/TXD

31

P3

6

/AEVH

P3

7

/AEVL

P5

0

/

WKP

0

/SEG

1

P5

1

/

WKP

1

/SEG

2

P5

2

/

WKP

2

/SEG

3

P5

3

/

WKP

3

/SEG

4

P5

4

/

WKP

4

/SEG

5

P5

5

/

WKP

5

/SEG

6

P5

6

/

WKP

6

/SEG

7

P5

7

/

WKP

7

/SEG

8

P4

0

/SCK

32

P4

1

/RXD

32

P4

2

/TXD

32

P4

3

/

IRQ

0

OSC

1

OSC

2

System Clock

OSC

Port 1

Port A

Port 8

Port 7

Port 6

Port 3

Port 4

Port 5

X

1

X

2

Sub Clock

OSC

V

SS

V

SS

V

CC

CV

CC

RES

TEST

H8/300L

CPU

LCD Power

Supply

ROM

(60k/48k/40k/32k

24k/16k)

RAM

(2k/1k)

Timer - A

Timer - C

Timer - F

Timer - G

Asynchronous

counter

Serial

communication

interface 3-1

Serial

communication

interface 3-2

14-bit

PWM

WDT

LCD

Controller

A/D

(10bit)

V

0

V

1

V

2

V

3

PA

3

/COM

4

PA

2

/COM

3

PA

1

/COM

2

PA

0

/COM

1

P8

7

/SEG

32

/CL

1

P8

6

/SEG

31

/CL

2

P8

5

/SEG

30

/DO

P8

4

/SEG

29

/M

P8

3

/SEG

28

P8

2

/SEG

27

P8

1

/SEG

26

P8

0

/SEG

25

P7

7

/SEG

24

P7

6

/SEG

23

P7

5

/SEG

22

P7

4

/SEG

21

P7

3

/SEG

20

P7

2

/SEG

19

P7

1

/SEG

18

P7

0

/SEG

17

P6

7

/SEG

16

P6

6

/SEG

15

P6

5

/SEG

14

P6

4

/SEG

13

P6

3

/SEG

12

P6

2

/SEG

11

P6

1

/SEG

10

P6

0

/SEG

9

Port B

AV

CC

AV

SS

PB

0

/AN

0

PB

1

/AN

1

PB

2

/AN

2

PB

3

/AN

3

PB

4

/AN

4

PB

5

/AN

5

PB

6

/AN

6

PB

7

/AN

7

Figure 1.1 Block Diagram