32

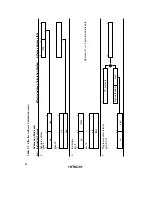

Figure 2.6 shows the instruction code format of arithmetic, logic, and shift instructions.

15

0

8

7

op

rm

rn

ADD, SUB, CMP,

ADDX, SUBX (Rm)

Notation:

op:

rm, rn:

IMM:

Operation field

Register field

Immediate data

15

0

8

7

op

rn

ADDS, SUBS, INC, DEC,

DAA, DAS, NEG, NOT

15

0

8

7

op

rn

MULXU, DIVXU

rm

15

0

8

7

rn

IMM

ADD, ADDX, SUBX,

CMP (#XX:8)

op

15

0

8

7

op

rn

AND, OR, XOR (Rm)

rm

15

0

8

7

rn

IMM

AND, OR, XOR (#xx:8)

op

15

0

8

7

rn

SHAL, SHAR, SHLL, SHLR,

ROTL, ROTR, ROTXL, ROTXR

op

Figure 2.6 Arithmetic, Logic, and Shift Instruction Codes