61

AT94KAL Series FPSLIC

Rev. 1138G–FPSLI–11/03

Reset Sources

The embedded AVR core has five sources of reset:

•

External Reset. The MCU is reset immediately when a low-level is present on the RESET

or AVR RESET pin.

•

Power-on Reset. The MCU is reset upon chip power-up and remains in reset until the

FPGA configuration has entered Idle mode.

•

Watchdog Reset. The MCU is reset when the Watchdog Timer period expires and the

watchdog is enabled.

•

Software Reset. The MCU is reset when the SRST bit in the Software Control register is

set (one).

•

JTAG AVR Reset. The MCU is reset as long as there is a logic one in the Reset Register,

one of the scan chains of the JTAG system. See “IEEE 1149.1 (JTAG) Boundary-scan” on

page 73.

During reset, all I/O registers except the MCU Status register are then set to their Initial Val-

ues, and the program starts execution from address $0000. The instruction placed in address

$0000 must be a JMP – absolute jump instruction to the reset handling routine. If the program

never enables an interrupt source, the interrupt vectors are not used, and regular program

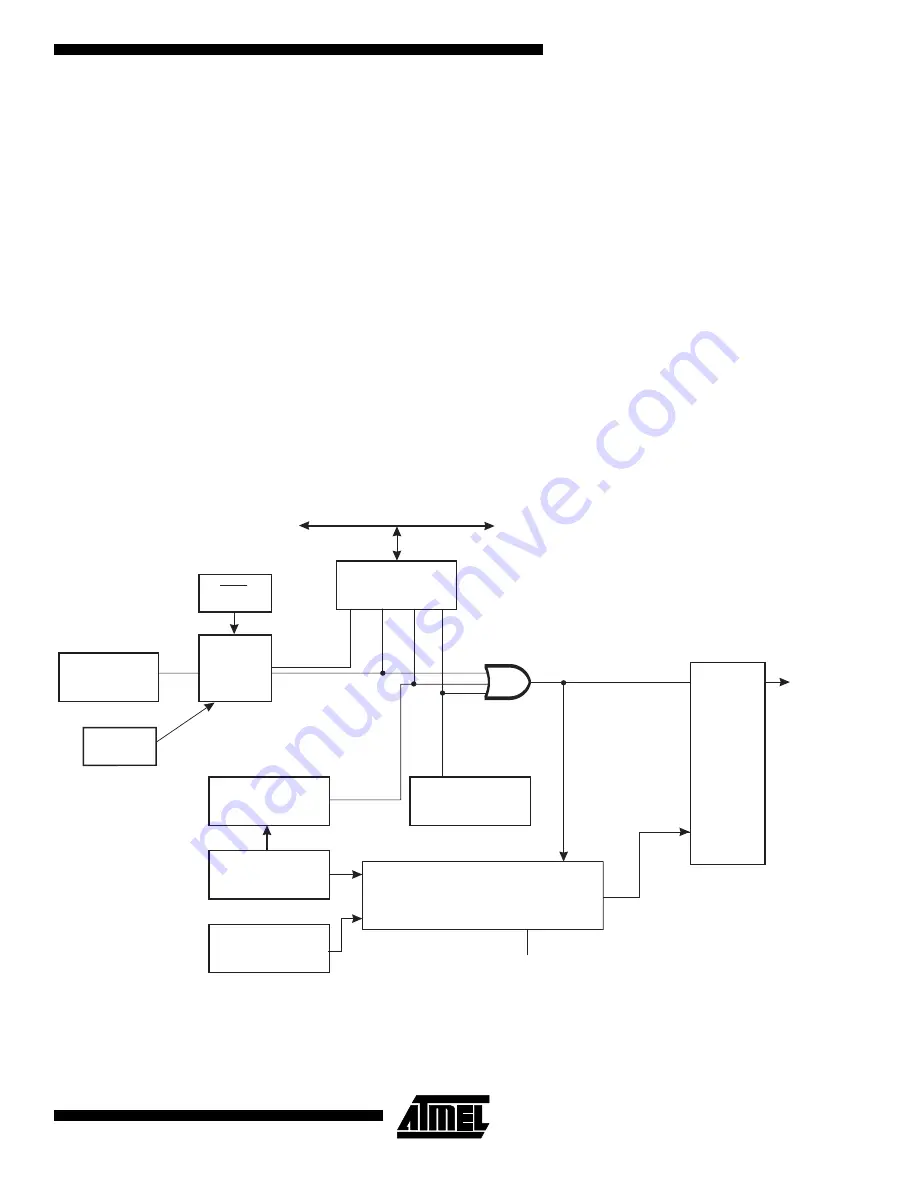

code can be placed at these locations. The circuit diagram in Figure 35 shows the reset logic.

Table 16 defines the timing and electrical parameters of the reset circuitry.

Figure 35.

Reset Logic

MCU STATUS

DATA BUS

RESET/

AVR RESET

WATCHDOG

TIMER

INTERNAL

OSCILLATOR

SYSTEM

CLOCK

DELAY COUNTERS

Q

S

R

INTERNAL

RESET

POR

COUNTER RESET

SEL [4:0] CONTROLLED

BY FPGA CONFIGURATION

FULL

FPGA

CONFIG

LOGIC

EXTRF

WDRF

SFTCR

BIT 0

PORF

JTAG RESET

REGISTER

JT RF