91

AT94KAL Series FPSLIC

Rev. 1138G–FPSLI–11/03

The output compare registers are 8-bit read/write registers. The Timer/Counter Output Com-

pare Registers contains the data to be continuously compared with the Timer/Counter. Actions

on compare matches are specified in TCCR0 and TCCR2. A compare match does only occur

if the Timer/Counter counts to the OCR value. A software write that sets Timer/Counter and

Output Compare Register to the same value does not generate a compare match.

A compare match will set the compare interrupt flag in the CPU clock-cycle following the com-

pare event.

Timer/Counter 0 and 2

in PWM Mode

When PWM mode is selected, the Timer/Counter either wraps (overflows) when it reaches

$FF or it acts as an up/down counter.

If the up/down mode is selected, the Timer/Counter and the Output Compare Registers –

OCR0 or OCR2 form an 8-bit, free-running, glitch-free and phase correct PWM with outputs on

the PE1(OC0/PWM0) or PE3(OC2/PWM2) pin.

If the overflow mode is selected, the Timer/Counter and the Output Compare Registers –

OCR0 or OCR2 form an 8-bit, free-running and glitch-free PWM, operating with twice the

speed of the up/down counting mode.

PWM Modes (Up/Down

and Overflow)

The two different PWM modes are selected by the CTC0 or CTC2 bit in the Timer/Counter

Control Registers – TCCR0 or TCCR2 respectively.

If CTC0/CTC2 is cleared and PWM mode is selected, the Timer/Counter acts as an up/down

counter, counting up from $00 to $FF, where it turns and counts down again to zero before the

cycle is repeated. When the counter value matches the contents of the Output Compare Reg-

ister, the PE1(OC0/PWM0) or PE3(OC2/PWM2) pin is set or cleared according to the settings

of the COMn1/COMn0 bits in the Timer/Counter Control Registers TCCR0 or TCCR2.

If CTC0/CTC2 is set and PWM mode is selected, the Timer/Counters will wrap and start

counting from $00 after reaching $FF. The PE1(OC0/PWM0) or PE3(OC2/PWM2) pin will be

set or cleared according to the settings of COMn1/COMn0 on a Timer/Counter overflow or

when the counter value matches the contents of the Output Compare Register. Refer to Table

25 for details.

Notes:

1. n = 0 or 2

2. x = don’ t care

In PWM mode, the value to be written to the Output Compare Register is first transferred to a

temporary location, and then latched into the OCR when the Timer/Counter reaches $FF. This

prevents the occurrence of odd-length PWM pulses (glitches) in the event of an unsynchro-

nized OCR0 or OCR2 write. See Figure 52 and Figure 53 for examples.

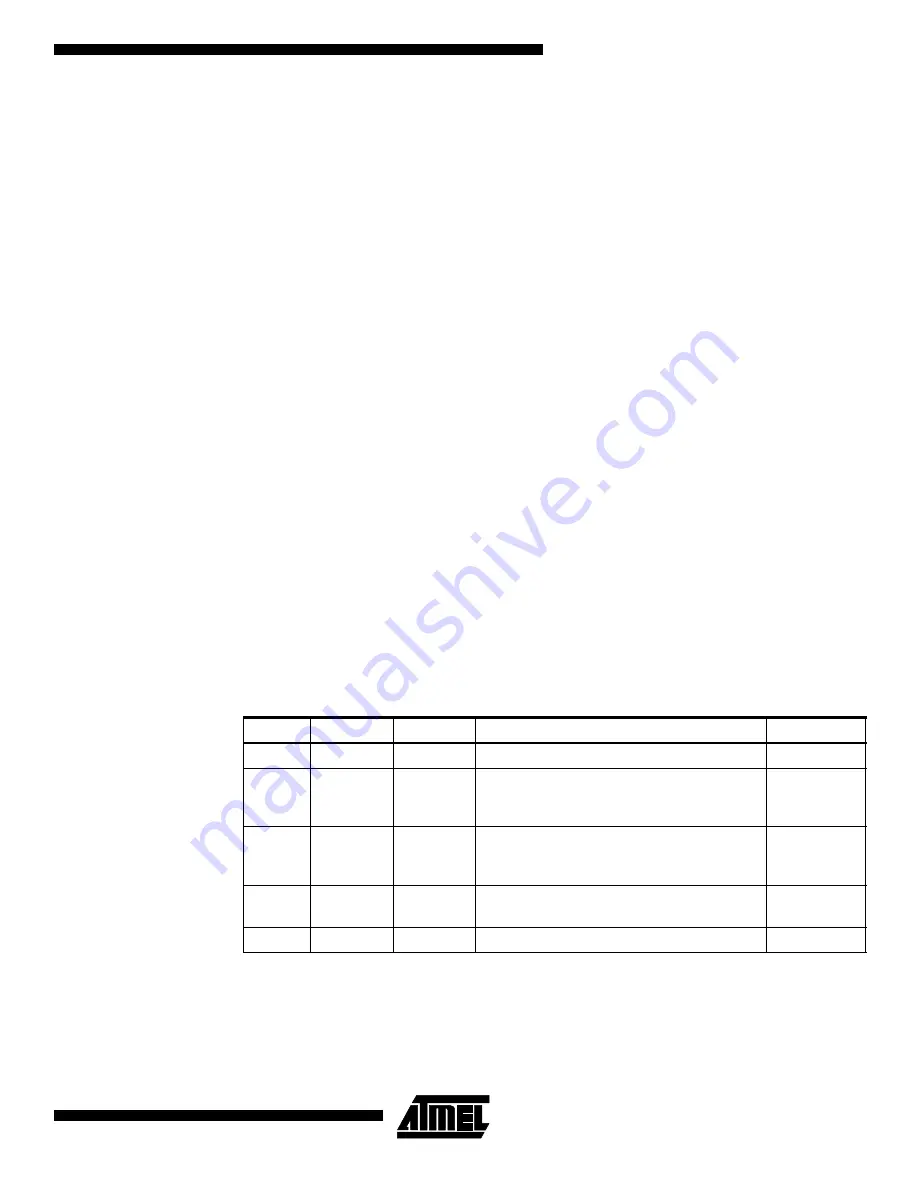

Table 25.

Compare Mode Select in PWM Mode

CTCn

COMn1

COMn0

Effect on Compare Pin

Frequency

x

0

x

Not connected

–

0

1

1

Cleared on compare match, up-counting. Set

on compare match, down-counting (non-

inverted PWM)

f

TCK0/2

/510

0

1

1

Cleared on compare match, down-counting.

Set on compare match, up-counting (inverted

PWM)

f

TCK0/2

/510

1

1

0

Cleared on compare match,

set on overflow

f

TCK0/2

/256

1

1

1

Set on compare match, set on overflow

f

TCK0/2

/256