AT32F421

Series Reference Manual

2022.11.11

Page 221

Rev 2.02

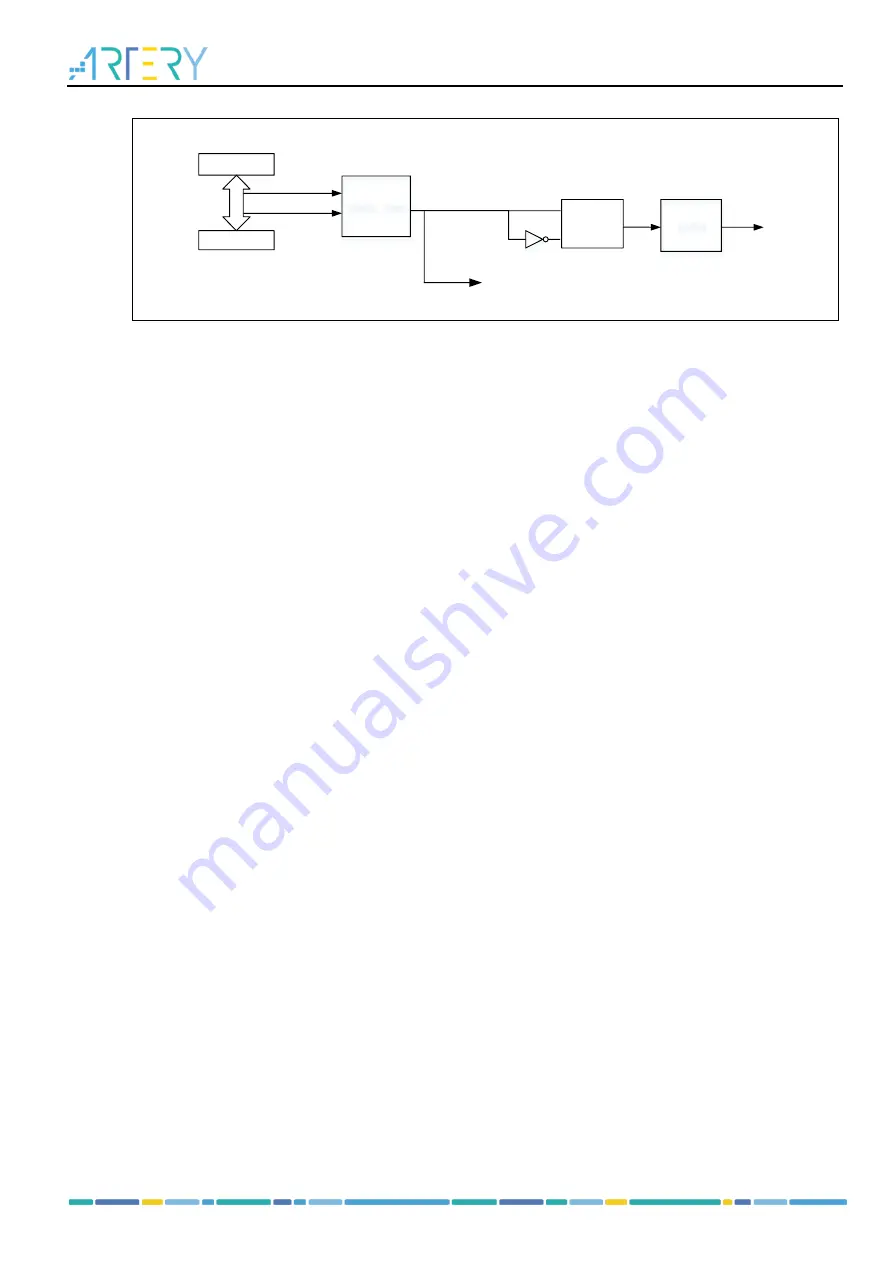

Figure 14-65 Channel 2 output stage

TMRx_CM1

C2ORAW

C2EN

C2OUT

CNT_value>C2DT

CNT_value=C2DT

To the master mode

controller

CNT_value

C2DT

Compare

C2P

Output mode

controller

Polarity

selection

Output enable

Output mode

Write CxC[2: 0]≠2’b00 to configure the channel as output to implement multiple output modes. In this

case, the counter value is compared with the value in the TMRx_CxDT register, and the intermediate

signal CxORAW is generated according to the output mode selected by CxOCTRL[2: 0], which is sent

to IO after being processed by the output control circuit. The period of the output signal is configured by

the TMRx_PR register, while the duty cycle by the TMR15_CxDT register.

Output compare modes include:

PWM mode A:

Set CxOCTRL=3’b110 to enable PWM mode A. In upcounting, when

TMRx_C1DT>TMRx_CVAL, C1ORAW outputs high; otherwise, outputs low. In downcounting,

when TMRx_C1DT<TMRx_CVAL, C1ORAW outputs low; otherwise, outputs high. T To set PWM

mode A, the following process is recommended:

–

Set the TMRx_PR register to set PWM period;

–

Set the TMRx_CxDT register to set PWM duty cycle;

–

Set CxOCTRL=3

’b110 in the TMRx_CM1/CM2 register and set output mode as PWM mode A;

–

Set the TMRx_DIV register to set the counting frequency;

–

Set the TWCMSEL[1:0] bit in the TMRx_CTRL1 register to set the count mode;

–

Set CxP bit and CxCP bit in the TMRx_CCTRL register to set output polarity;

–

Set CxEN bit and CxCEN bit in the TMRx_CCTRL register to enable channel output;

–

Set the OEN bit in the TMRx_BRK register to enable TMRx output;

–

Set the corresponding GPIO of TMR output channel as the multiplexed mode;

–

Set the TMREN bit in the TMRx_CTRL1 register to enable TMRx counter.

PWM mode B:

Set CxOCTRL=3’b111 to enable PWM mode B. In upcounting, when

TMRx_C1DT>TMRx_CVAL, C1ORAW outputs low; otherwise, outputs high. In downcounting,

when TMRx_C1DT<TMRx_CVAL, C1ORAW outputs high; otherwise, outputs low.

Forced output mode:

Set CxOCTRL=3’b100/101 to enable forced output mode. In this case, the

CxORAW is forced to be the programmed level, irrespective of the counter value. Despite this,

the channel flag bit and DMA request still depend on the compare result.

Output compare mode:

Set CxOCTRL=3’b001/010/011 to enable output compare mode. In this

case, when the counter value matches the value of the CxDT register, the CxORAW is forced

high (CxOCTRL=3’b001), low (CxOCTRL=3’b010) or toggling (CxOCTRL=3’b011).

One-pulse mode:

This is a particular case of PWM mode. Set OCMEN=1 to enable one-pulse

mode. In this mode, the comparison match is performed in the current counting period. The

TMREN bit is cleared as soon as the current counting is completed. Therefore, only one pulse is

output. When configured as in upcounting mode, the configuration must follow the rule:

CVAL<CxDT≤PR; in downcounting mode, CVAL>CxDT is required.

Fast output mode:

Set CxOIEN=1 to enable this mode. If enabled, the CxORAW signal will not

change when the counter value matches the CxDT, but at the beginning of the current counting

period. In other words, the comparison result is advanced, so the comparison result between the

counter value and the CxDT register will determine the level of CxORAW in advance.