lator or an off-chip crystal oscillator. The off-chip oscillator can also drive the high-frequency

clock directly.

For the FE310-G000, the TileLink bus clock (

tlclk

) is fixed to be the same as the processor

core clock (

coreclk

).

The Always-On block includes a real-time clock circuit that is driven from one of the low-fre-

quency clock sources: an off-chip oscillator (LFOSC) or an an on-chip low-frequency oscillator

(LFROSC).

6.2

PRCI Address Space Usage

PRCI (Power, Reset, Clock, Interrupt) is an umbrella term for platform non-AON memory-

mapped control and status registers controlling component power states, resets, clock selection,

and low-level interrupts, hence the name. The AON block contains registers with similar func-

tions, but only for the AON block units.

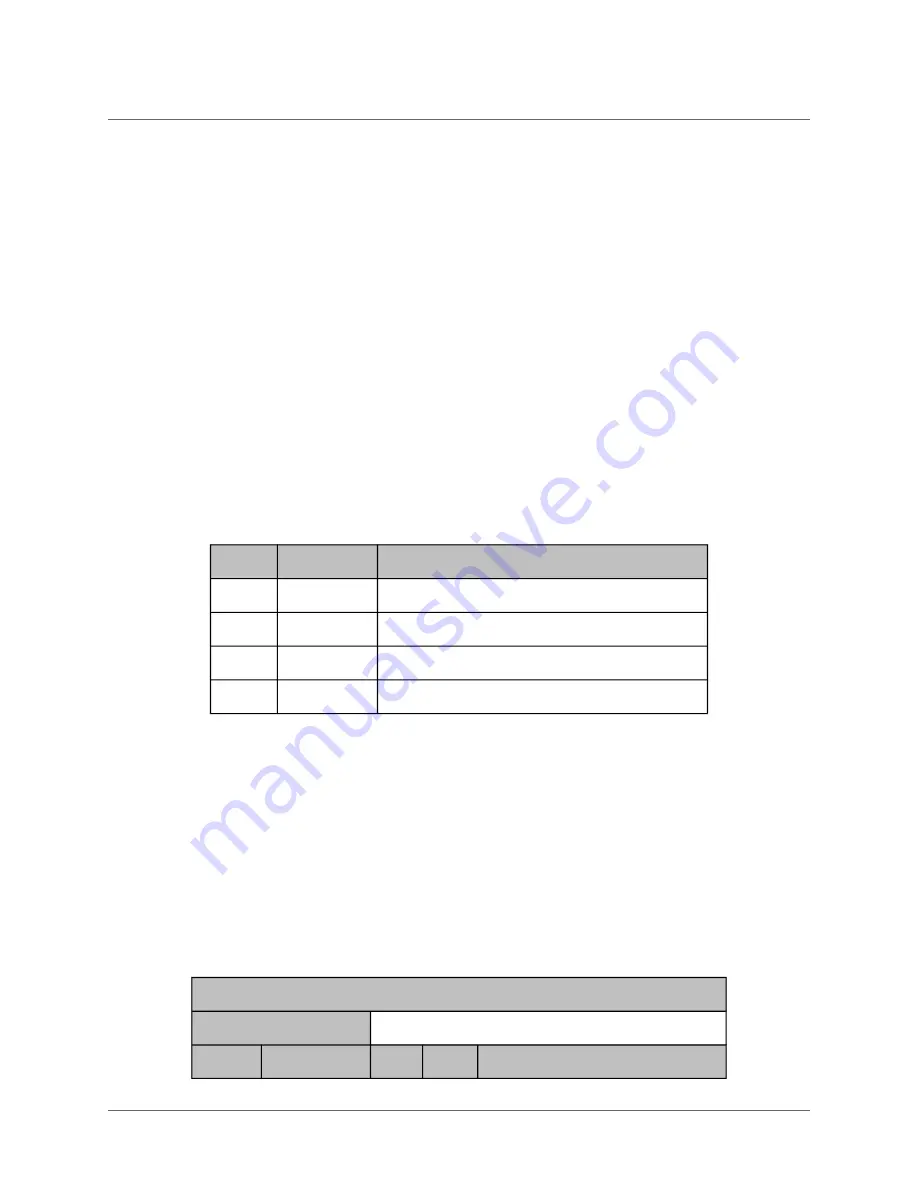

Table 4 shows the memory map for the PRCI on the FE310-G000.

Offset

Name

Description

0x0

hfrosccfg

Ring Oscillator Configuration and Status

0x4

hfxosccfg

Crystal Oscillator Configuration and Status

0x8

pllcfg

PLL Configuration and Status

0xC

plloutdiv

PLL Final Divide Configuration

6.3

Internal Trimmable Programmable 72 MHz Oscillator

(HFROSC)

An internal trimmable high-frequency ring oscillator (HFROSC) is used to provide the default

clock after reset, and can be used to allow operation without an external high-frequency crystal

or the PLL.

The oscillator is controlled by the

hfrosccfg

register, which is memory-mapped in the PRCI

address space, and whose format is shown in Table 5.

hfrosccfg: Ring Oscillator Configuration and Status (

hfrosccfg

)

Register Offset

0x0

Bits

Field Name

Attr.

Rst.

Description

Table 4:

SiFive PRCI memory map, offsets relative to PRCI base address.

Table 5:

hfrosccfg: Ring Oscillator Configuration and Status

Chapter 6 Clock Generation

SiFive FE310-G000 Manual: v3p2

© SiFive, Inc.

Page 23

Содержание FE310-G000

Страница 1: ...SiFive FE310 G000 Manual v3p2 SiFive Inc ...