Chapter 17

Universal Asynchronous Receiver/

Transmitter (UART)

This chapter describes the operation of the SiFive Universal Asynchronous Receiver/Transmit-

ter (UART).

17.1

UART Overview

The UART peripheral supports the following features:

• 8-N-1 and 8-N-2 formats: 8 data bits, no parity bit, 1 start bit, 1 or 2 stop bits

• 8-entry transmit and receive FIFO buffers with programmable watermark interrupts

• 16× Rx oversampling with 2/3 majority voting per bit

The UART peripheral does not support hardware flow control or other modem control signals, or

synchronous serial data transfers.

17.2

UART Instances in FE310-G000

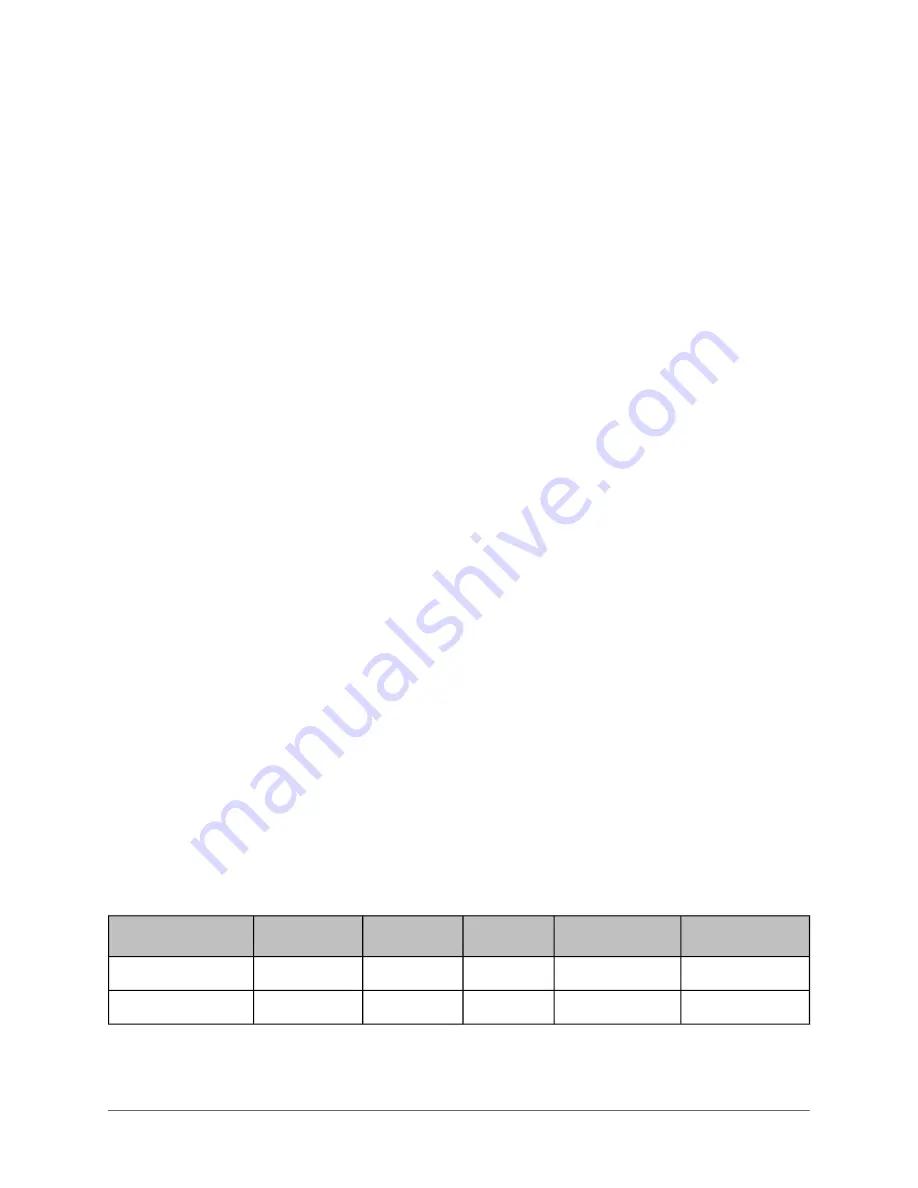

FE310-G000 contains two UART instances. Their addresses and parameters are shown in

Table 48.

Table 48:

UART Instances

Instance Num-

ber

Address

div_width

div_init

TX FIFO

Depth

RX FIFO

Depth

0

0x10013000

16

3

8

8

1

0x10023000

16

3

8

8

SiFive FE310-G000 Manual: v3p2

© SiFive, Inc.

Page 76

Содержание FE310-G000

Страница 1: ...SiFive FE310 G000 Manual v3p2 SiFive Inc ...