Contents

1

Introduction

.............................................................................................................. 8

1.1

FE310-G000 Overview

................................................................................................ 8

1.2

E31 RISC‑V Core

..................................................................................................... 10

1.3

Interrupts

................................................................................................................. 10

1.4

On-Chip Memory System

........................................................................................... 10

1.5

Always-On (AON) Block

............................................................................................ 10

1.6

GPIO Complex

......................................................................................................... 11

1.7

Universal Asynchronous Receiver/Transmitter

.............................................................11

1.8

Hardware Serial Peripheral Interface (SPI)

..................................................................11

1.9

Pulse Width Modulation

............................................................................................. 11

1.10

Debug Support

....................................................................................................... 11

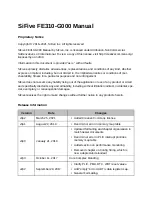

2

List of Abbreviations and Terms

.................................................................13

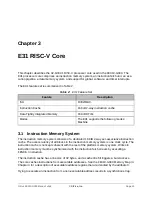

3

E31 RISC-V Core

.................................................................................................. 15

3.1

Instruction Memory System

........................................................................................ 15

3.2

Instruction Fetch Unit

................................................................................................ 16

3.3

Execution Pipeline

.................................................................................................... 16

3.4

Data Memory System

................................................................................................ 17

3.5

Atomic Memory Operations

........................................................................................ 17

3.6

Hardware Performance Monitor

.................................................................................. 17

4

Memory Map

........................................................................................................... 18

5

Boot Process

.......................................................................................................... 20

5.1

Non-volatile Code Options

......................................................................................... 20

5.1.1

Gate ROM (GROM)

.......................................................................................... 20

5.1.2

Mask ROM (MROM)

......................................................................................... 20

5.1.3

One-Time Programmable (OTP) Memory

...........................................................21

SiFive FE310-G000 Manual: v3p2

© SiFive, Inc.

Page 1

Содержание FE310-G000

Страница 1: ...SiFive FE310 G000 Manual v3p2 SiFive Inc ...